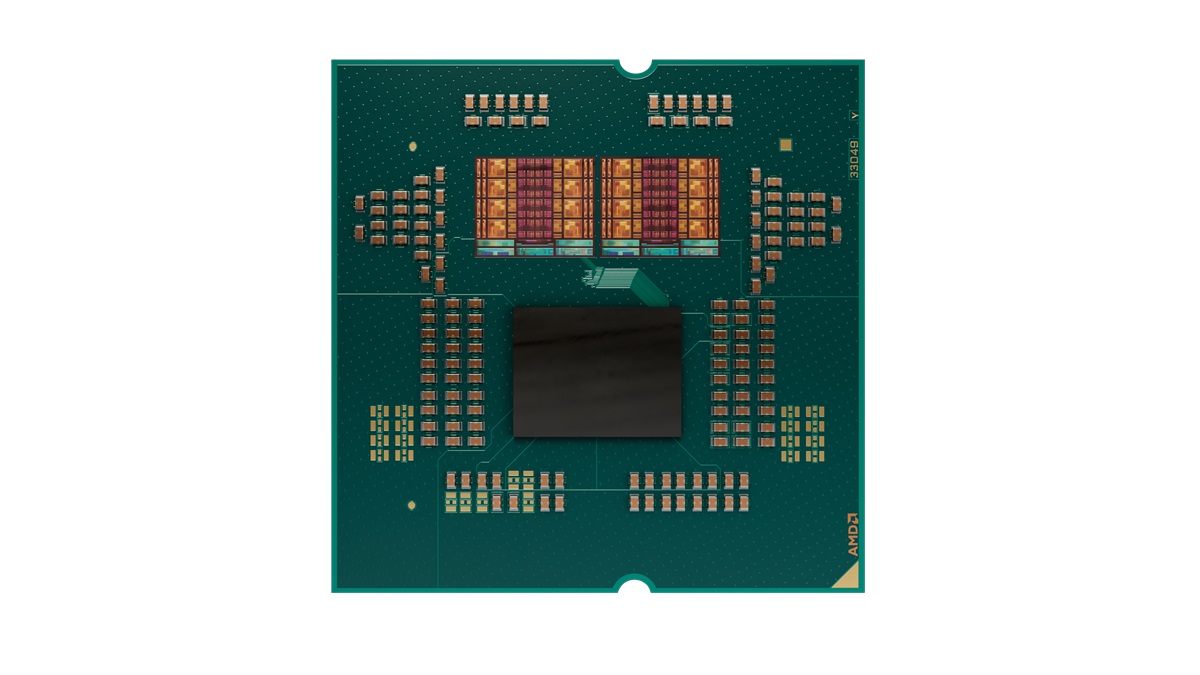

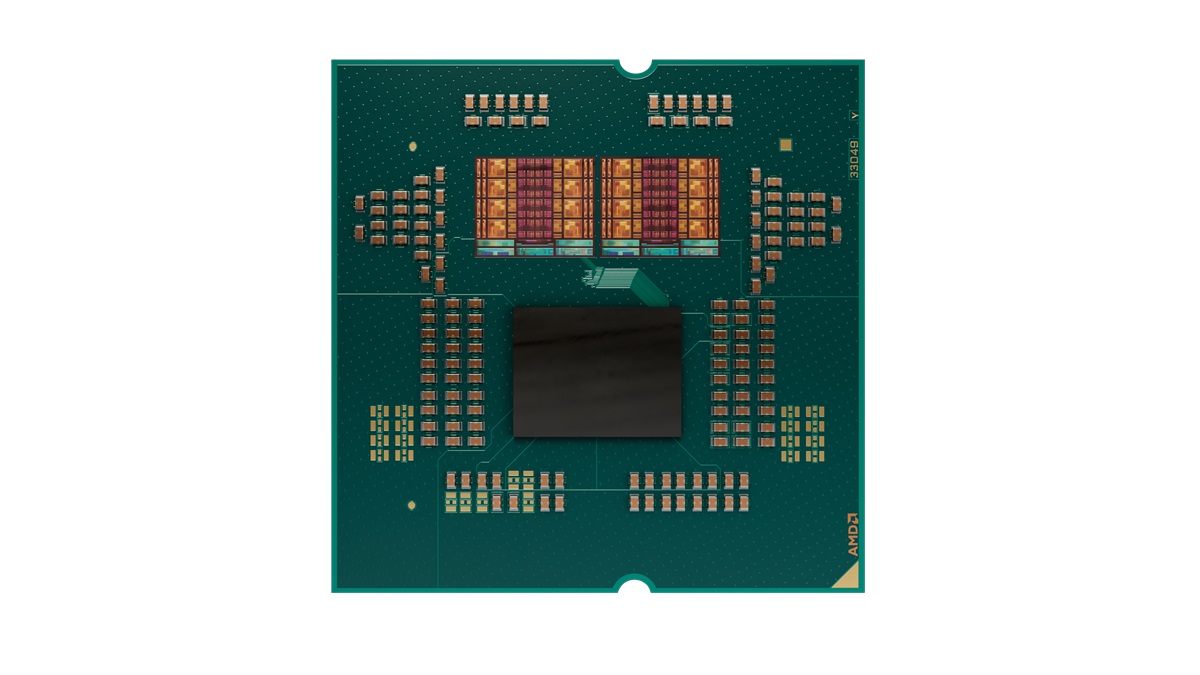

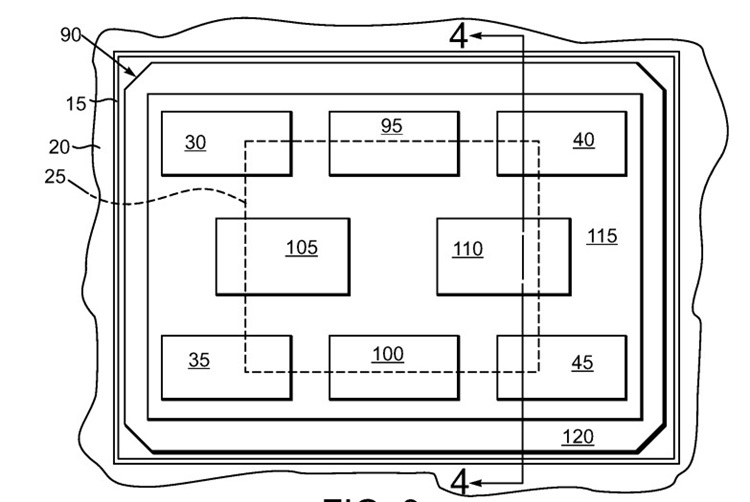

AMD 最近提交了一項新專利,揭示了在未來 Ryzen SoC 中實現「多晶片堆疊」的計劃,屬於一種新穎的封裝設計,透過使晶片部分重疊來實現緊湊的晶片堆疊和互連。

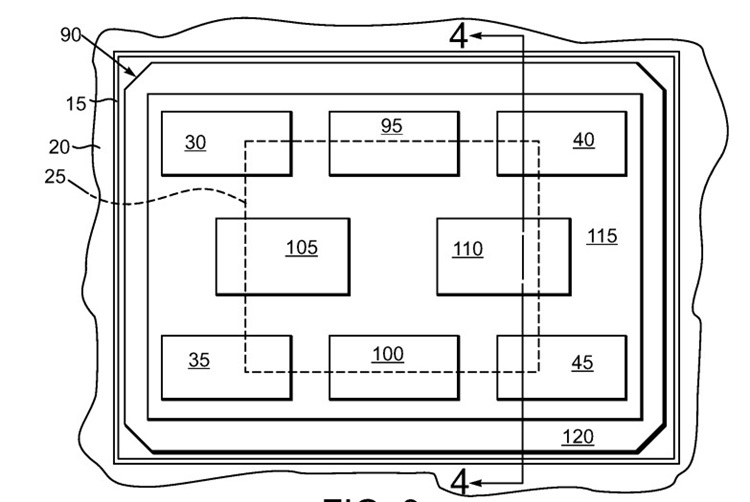

根據AMD的介紹,將較小的小晶片與較大的晶片部分重疊,為同一晶片上的其他組件和功能創造空間。

新方法旨在提高接觸區域的效率,從而在相同的晶片尺寸內為更高的核心數、更大的快取、以及為增加的記憶體頻寬騰出空間。新的堆疊技術將透過重疊的小晶片來減少組件之間的物理距離,最大限度地減少互連延遲,並實現不同晶片部分之間的更快通訊。該設計還將改進電源管理,因為分離的小晶片允許透過電源門控更好地控制每個單元。

引進 3D V-Cache 技術的 X3D 系列處理器在消費市場取得了成功,而資料中心產品更是將競爭對手 Intel 拋在了身後,預計新的堆疊方法會在未來的 AMD EPYC / Ryzen 產品裡發揮重要作用。過去幾年裡,AMD 致力於擺脫單晶片設計,走上了 3D chiplet 的道路。由於設計更為複雜,要完成從專利到設計、生產和最終產品的過程,可能需要等待較長時間。

來源

根據AMD的介紹,將較小的小晶片與較大的晶片部分重疊,為同一晶片上的其他組件和功能創造空間。

新方法旨在提高接觸區域的效率,從而在相同的晶片尺寸內為更高的核心數、更大的快取、以及為增加的記憶體頻寬騰出空間。新的堆疊技術將透過重疊的小晶片來減少組件之間的物理距離,最大限度地減少互連延遲,並實現不同晶片部分之間的更快通訊。該設計還將改進電源管理,因為分離的小晶片允許透過電源門控更好地控制每個單元。

引進 3D V-Cache 技術的 X3D 系列處理器在消費市場取得了成功,而資料中心產品更是將競爭對手 Intel 拋在了身後,預計新的堆疊方法會在未來的 AMD EPYC / Ryzen 產品裡發揮重要作用。過去幾年裡,AMD 致力於擺脫單晶片設計,走上了 3D chiplet 的道路。由於設計更為複雜,要完成從專利到設計、生產和最終產品的過程,可能需要等待較長時間。

來源