日前在ISSCC 2015研討會上,Samsung公佈了第二代3D V-NAND的部分細節,針對優化了的部分進行了一些解釋。

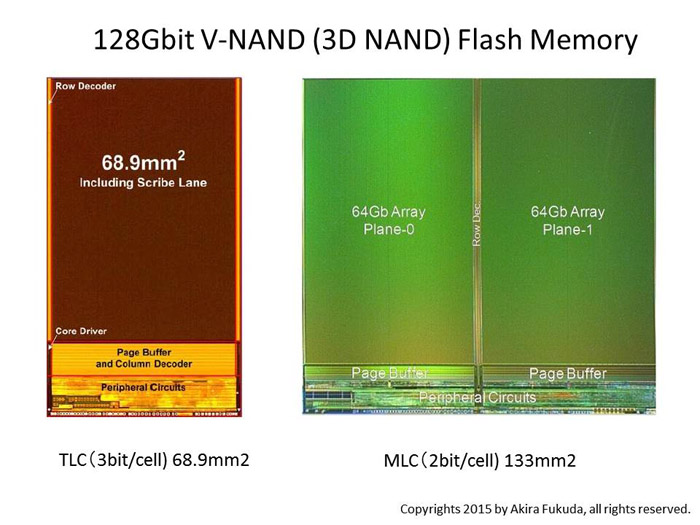

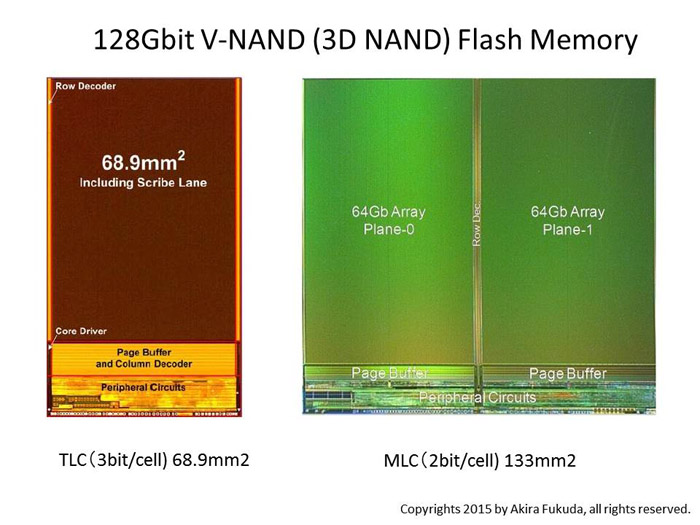

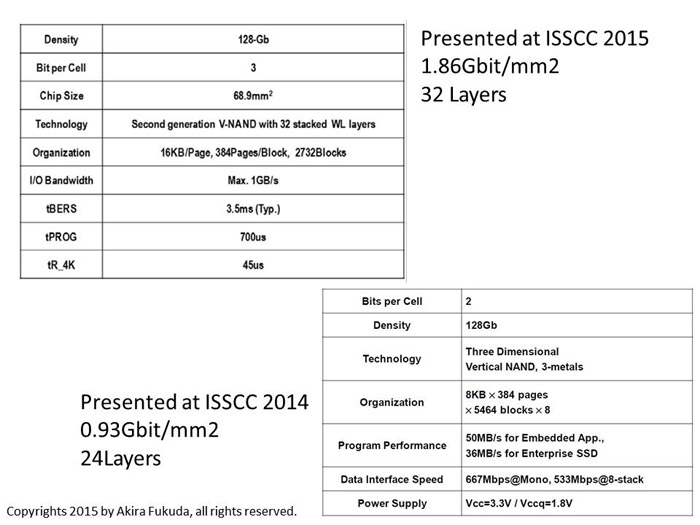

PC Watch對此進行了較為詳細的介紹,從上圖可以看到,第一代與第二代3D V-NAND在儲存密度上有很大的差異,第一代採用MLC設計,堆疊層數為24層,128Gbit容量所需面積為133mm2,而第二代採用TLC設計,堆疊層數上升至32層,儲存密度大幅提升,128Gb所佔面積為68.9mm2,第一代的儲存密度為0.93Gb/ mm2,第二代的就上升到1.86Gb/mm2,幅度達到了2.25倍,相對驚人。

兩代3D V-NAND儲存密度對比

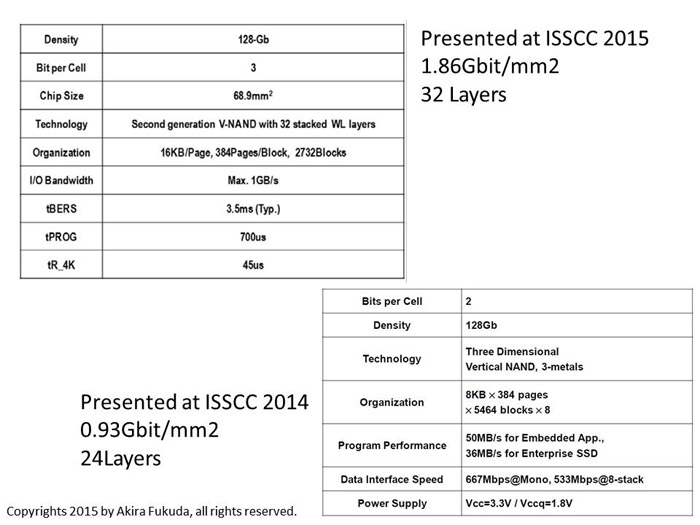

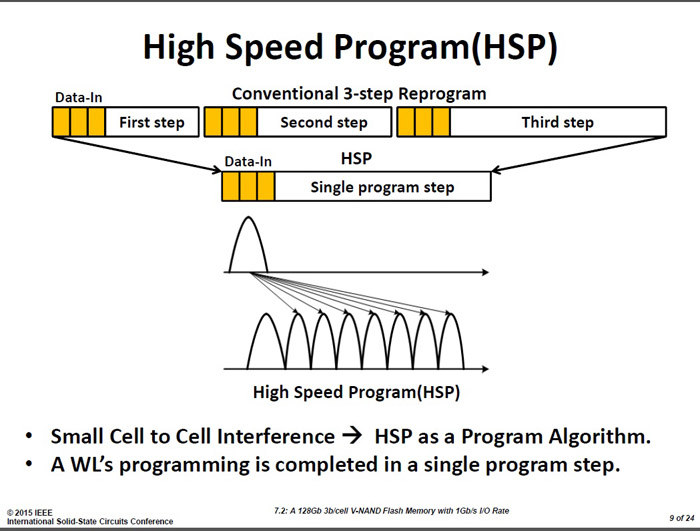

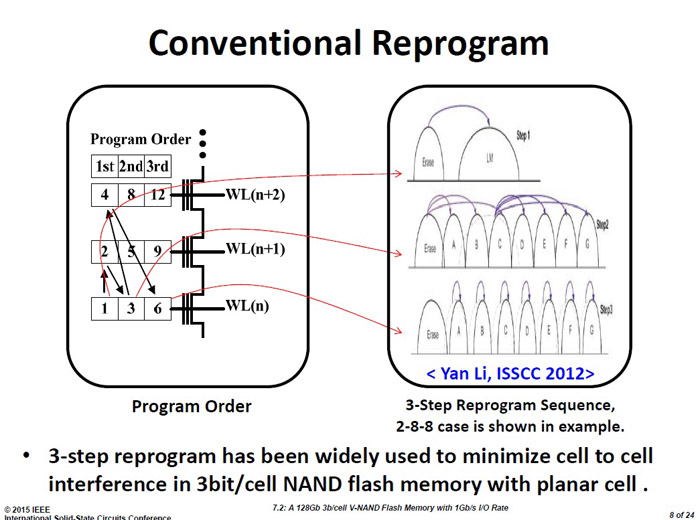

傳統的2D記憶體在達到一定密度之後每個電源儲存的電荷量會下降,另外相鄰的儲存單元也會產生電荷干擾,為了避免這些負面影響,傳統TLC的編程會拆分為三個階段,就是為了在編程時更為精確的控制電荷量。

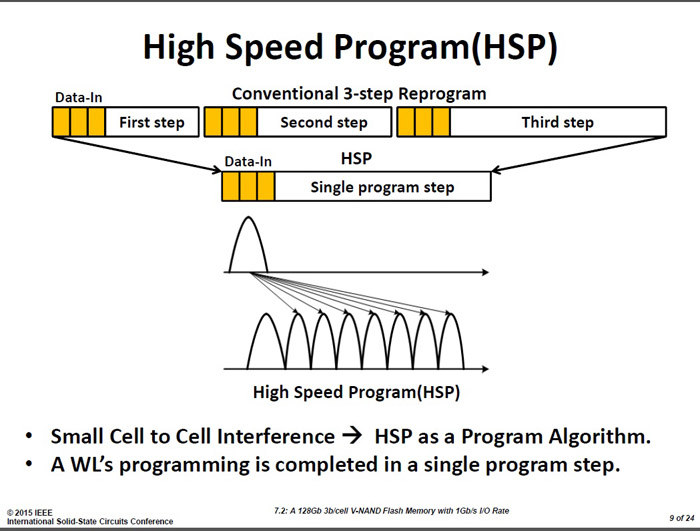

但是3D V-NAND就沒有傳統2D記憶體的問題,無需進行多階段控制,Samsung通過HSP技術將多階段編程過程整合為一個,記憶體編程時間大為減少。

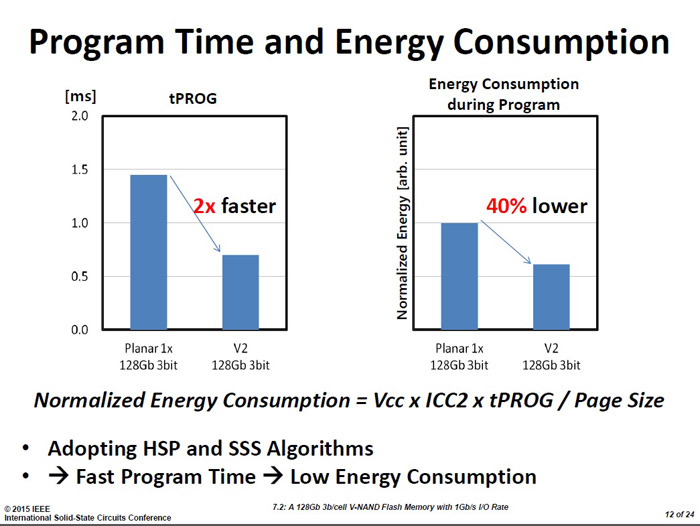

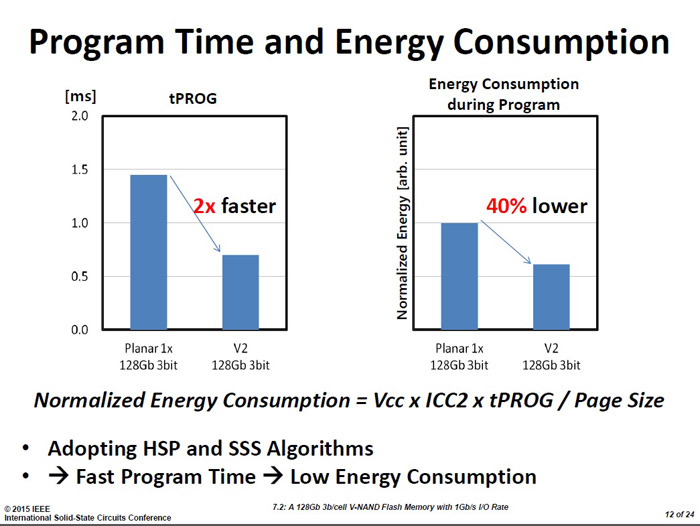

編程時間縮短為原來的二分之一,寫入功耗可以降低40%

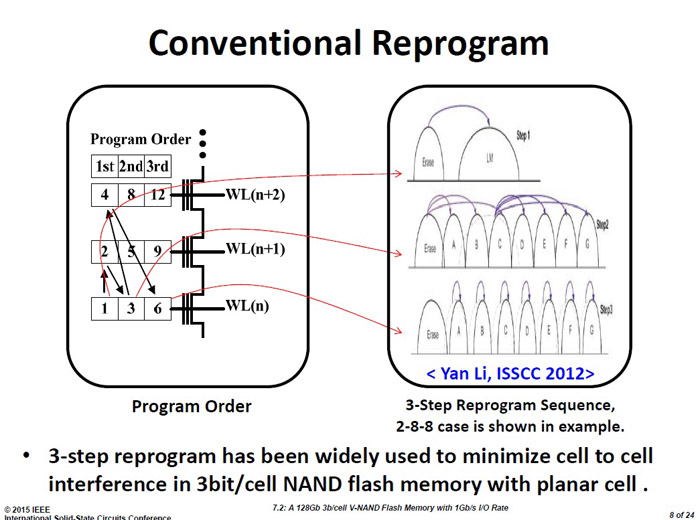

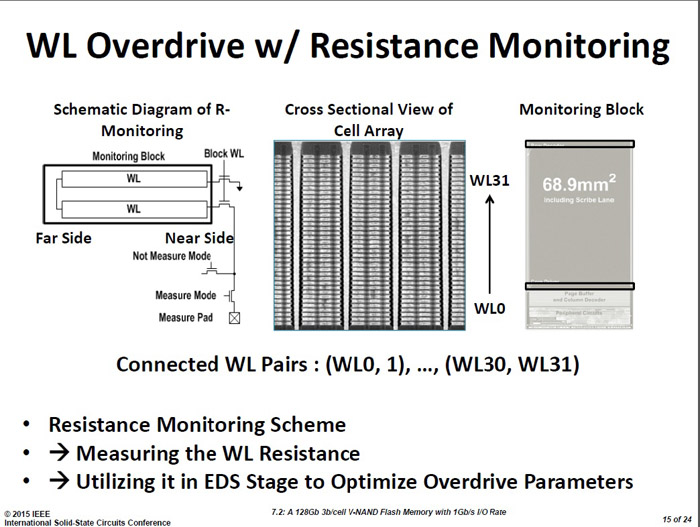

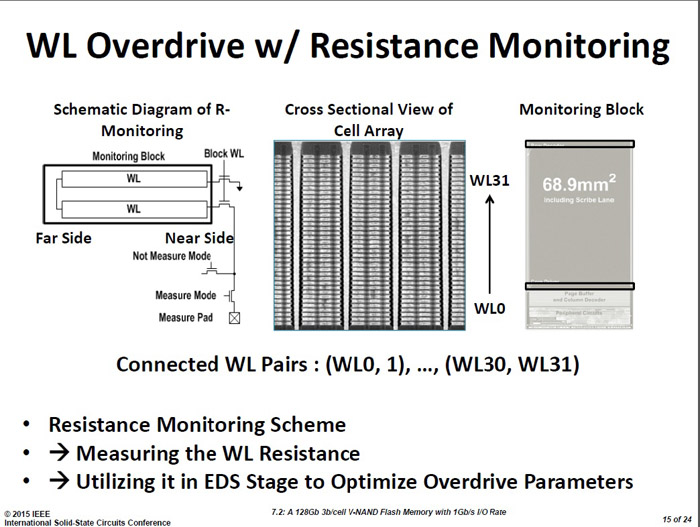

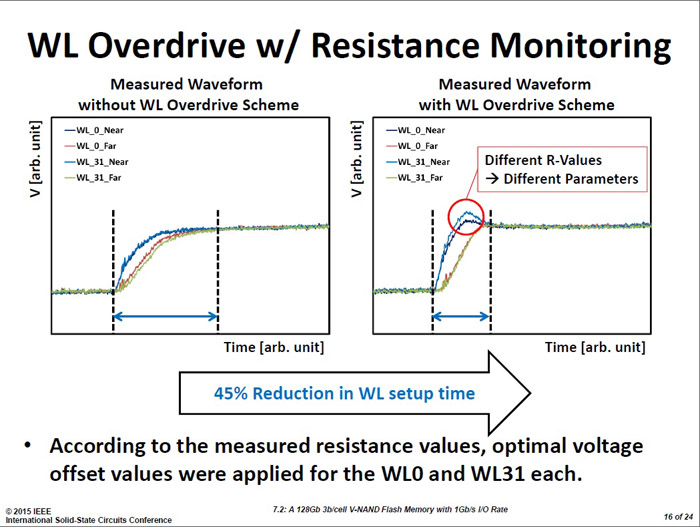

儲存核心的立體構造(中),Word line的阻值檢測(左)

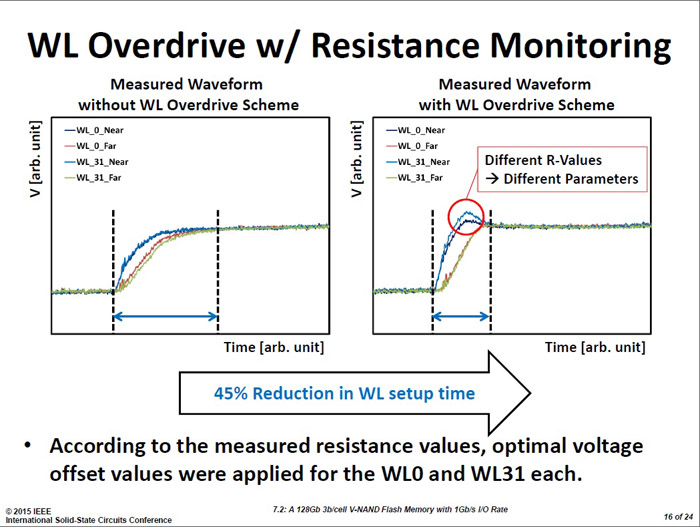

記憶體在結構上有所改變,造成了Word line在近段、遠端的阻值會有些差異,這樣的差異會造成讀取放大器與控制解碼間的遲滯,為了解決這樣的問題,進行了阻值檢測,以及針對不同的Word Line參數給予不同的電壓,這樣一來就能夠有效減低setup-time。

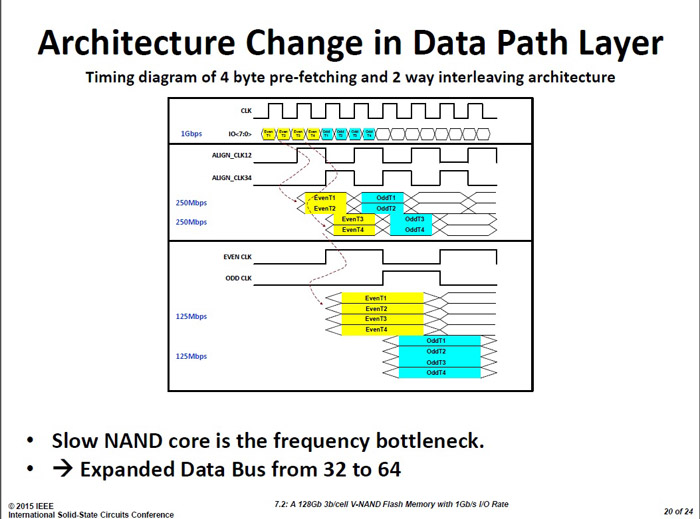

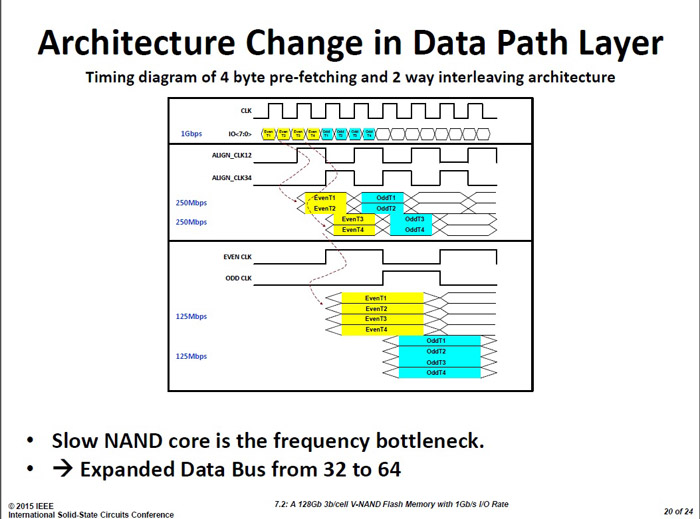

數據總線的架構圖,可實現1Gbps的高速數據傳速

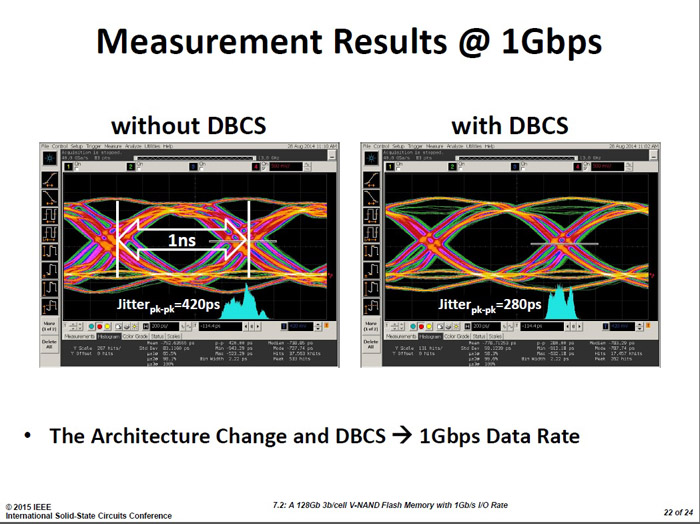

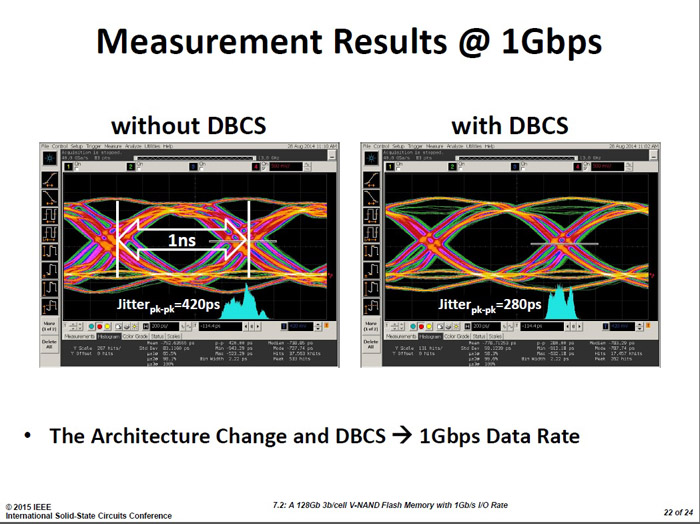

在讀寫方面,在4G數據預讀的同時,還會進行2路交錯的動作加速數據的傳送。還有在數據頻寬由原本的32Bit擴大到現在64Bit,然後根據傳輸速度的高低,晶片內部的電壓調節器進行電流調整以及電壓變動抑制,減少了信號的抖動,1Gbps下的抖動從420ps降低到280ps,這樣就實現了1Gbps的高速數據傳速。

來源:

http://www.expreview.com/39187.html

http://pc.watch.impress.co.jp/docs/news/event/20150305_691450.html

PC Watch對此進行了較為詳細的介紹,從上圖可以看到,第一代與第二代3D V-NAND在儲存密度上有很大的差異,第一代採用MLC設計,堆疊層數為24層,128Gbit容量所需面積為133mm2,而第二代採用TLC設計,堆疊層數上升至32層,儲存密度大幅提升,128Gb所佔面積為68.9mm2,第一代的儲存密度為0.93Gb/ mm2,第二代的就上升到1.86Gb/mm2,幅度達到了2.25倍,相對驚人。

兩代3D V-NAND儲存密度對比

傳統的2D記憶體在達到一定密度之後每個電源儲存的電荷量會下降,另外相鄰的儲存單元也會產生電荷干擾,為了避免這些負面影響,傳統TLC的編程會拆分為三個階段,就是為了在編程時更為精確的控制電荷量。

但是3D V-NAND就沒有傳統2D記憶體的問題,無需進行多階段控制,Samsung通過HSP技術將多階段編程過程整合為一個,記憶體編程時間大為減少。

編程時間縮短為原來的二分之一,寫入功耗可以降低40%

儲存核心的立體構造(中),Word line的阻值檢測(左)

記憶體在結構上有所改變,造成了Word line在近段、遠端的阻值會有些差異,這樣的差異會造成讀取放大器與控制解碼間的遲滯,為了解決這樣的問題,進行了阻值檢測,以及針對不同的Word Line參數給予不同的電壓,這樣一來就能夠有效減低setup-time。

數據總線的架構圖,可實現1Gbps的高速數據傳速

在讀寫方面,在4G數據預讀的同時,還會進行2路交錯的動作加速數據的傳送。還有在數據頻寬由原本的32Bit擴大到現在64Bit,然後根據傳輸速度的高低,晶片內部的電壓調節器進行電流調整以及電壓變動抑制,減少了信號的抖動,1Gbps下的抖動從420ps降低到280ps,這樣就實現了1Gbps的高速數據傳速。

來源:

http://www.expreview.com/39187.html

http://pc.watch.impress.co.jp/docs/news/event/20150305_691450.html