前言:

Intel長年在馬來西亞深耕晶圓封測,更於 2021年 12月時在馬來西亞投資約 71億美元的擴充計畫,這項投資旨在增強其在該地區的半導體製造和封裝測試能力,以應對不斷增長的需求並提升其在全球市場的競爭力,擴增的晶圓廠除了一般封裝測試的產線之外也會針對 Meteor Lake & Allow Lake (LGA1851)的 3D Foveros封裝;封裝測試是指將製造好的晶圓封裝在保護外殼內,以確保其在實際應用中的保護和運作,而半導體測試則是確保每個晶片都能正常運作並符合品質標準,這些封裝和測試工作是半導體製造過程中不可或缺的一部分,有助於確保最終產品的穩定性和可靠性;通常,這些工作也是半導體製造供應鏈中的重要環節之一,以確保製品能夠達到預期的性能和品質

滄者有幸也參加了 Intel 51年來首次開放媒體參訪的 Intel Technology Tour 2023 for 3D Advance ,Intel Technology Tour 2023活動聚焦在 Intel致力於創新策略與製造領域的領導地位,帶領全球媒體參訪 Intel位在馬來西亞的半導體封裝測試廠,並分享公司轉型策略「垂直整合製造模式 IDM 2.0」、最新技術發展,以及現場直擊即將發布的 Meteor Lake處理器的技術細節

Intel Penang封測廠

整個區域到處都是 Intel building,包含正在興建中並會在 2024啟用的封測廠房 (未來它將用於即將發布的 Meteor Lake、Arrow Lake和 Lunar Lake晶片上)

而在 Lab廠房到處都佈置有 Intel TECH Tour的 POP

參訪人員魚貫進場

途經 Crew的辦公室場景

參訪人群先安排到簡報室聽取簡報

參訪前的簡報

在介紹本次參訪的過程之前讓我們先來看看 Intel的 3D封裝測試技術的介紹

開場

概觀

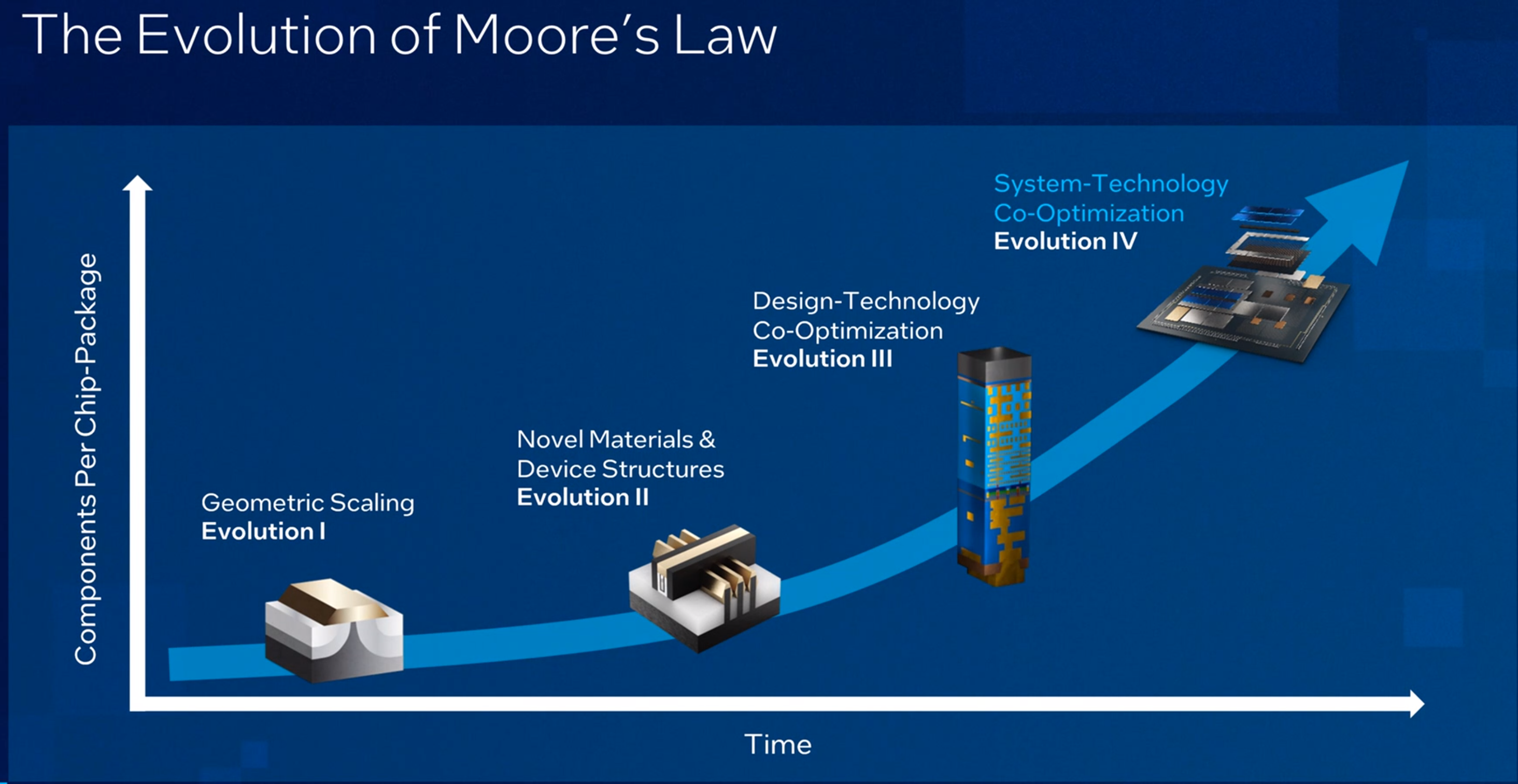

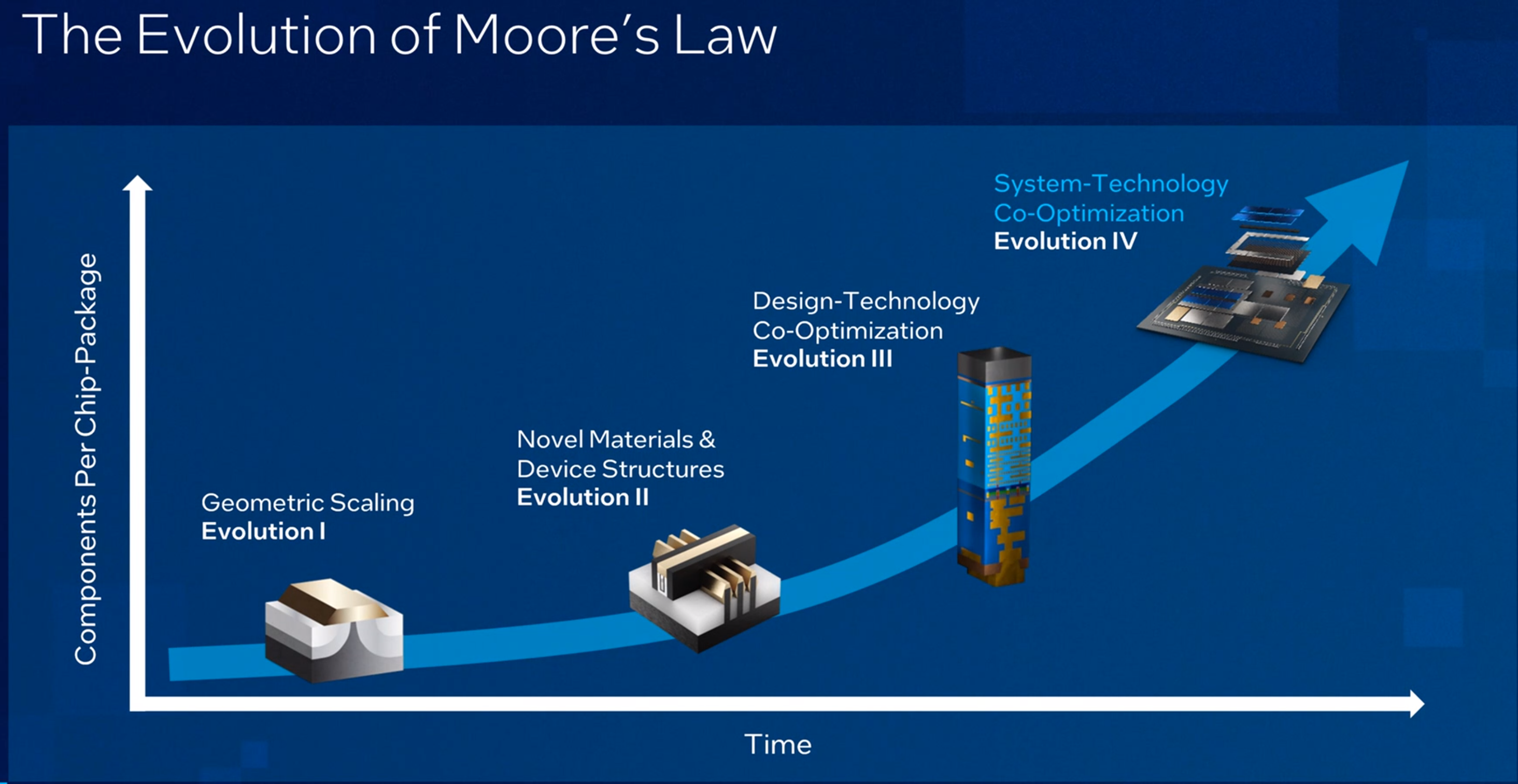

眾所皆知的依照 Intel Moore's Law,在當下一個 Chiplet可以容納 1千億個晶體管,而當電腦晶片正式進入 3D時代時,在 2030年時一個 Chiplet則將能容納有一萬億個電晶體

4年 5節點的 Moore's Law摩爾定律

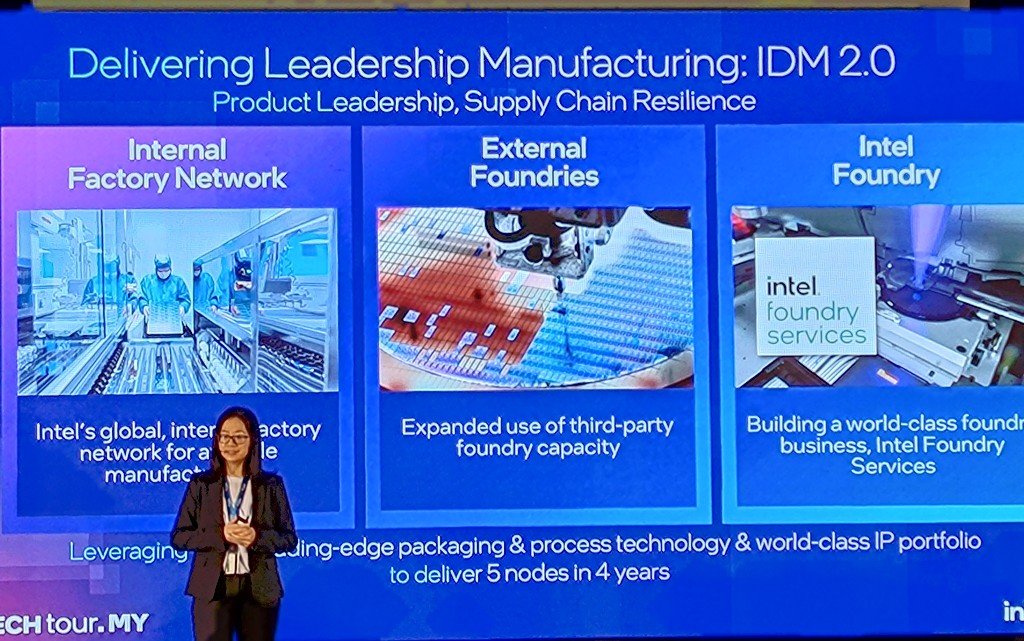

Steven Long提到 intel轉型的三大要素,第一點就是 Advancing Moore's Law,以 5N4D為主要目標

除了透過製程在同樣面積塞入更多電晶體之外,另一方面也透過先進封裝技術,在同樣的面積上透過 3D堆疊增加更多的運算能力,Moore在很久之前就有說過這樣的概念: 「It may prove to be more economical to build large systems out of smaller functions, which are separately packagedand interconnecte」

多重 Die的先進 3D封裝

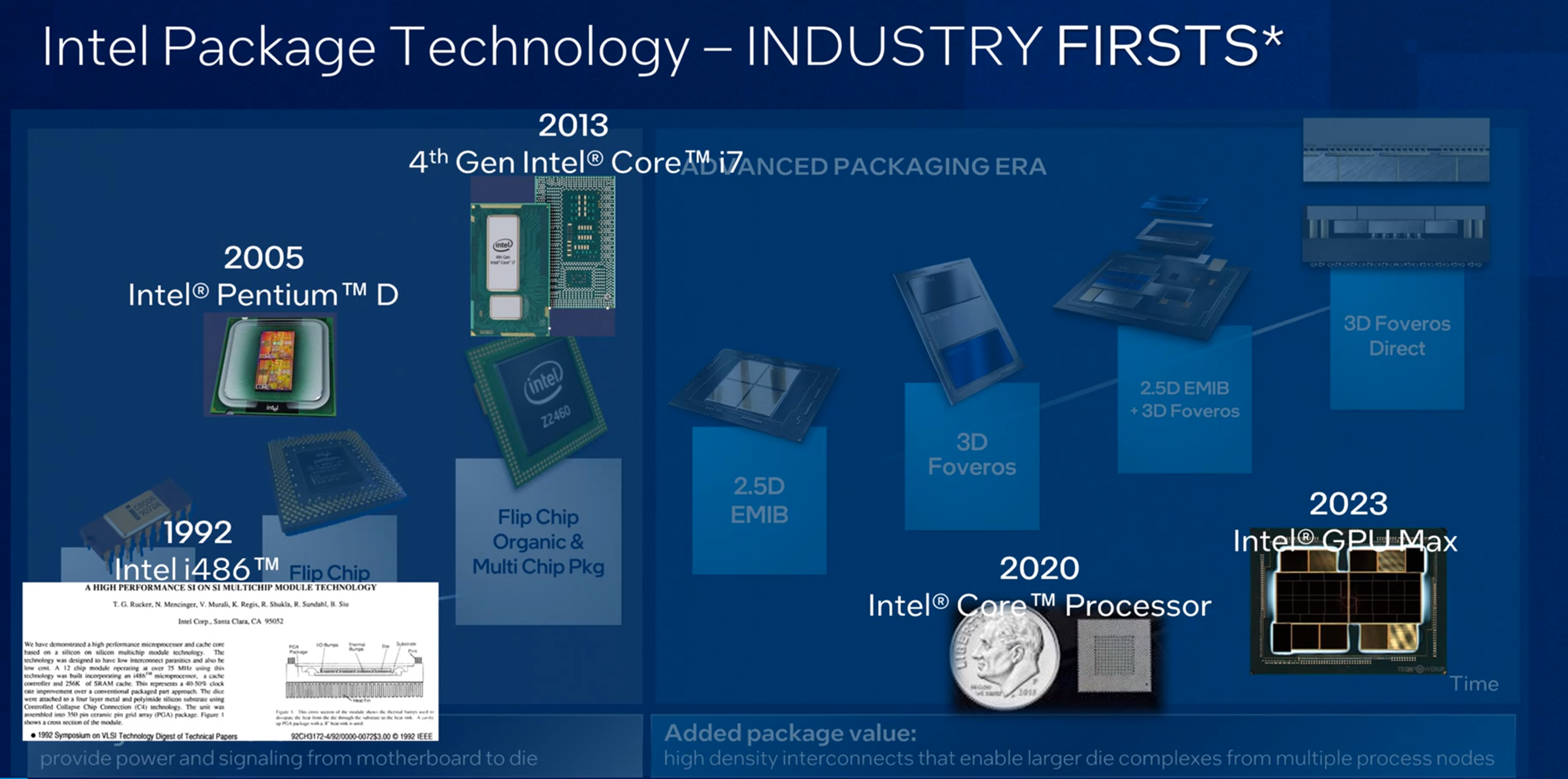

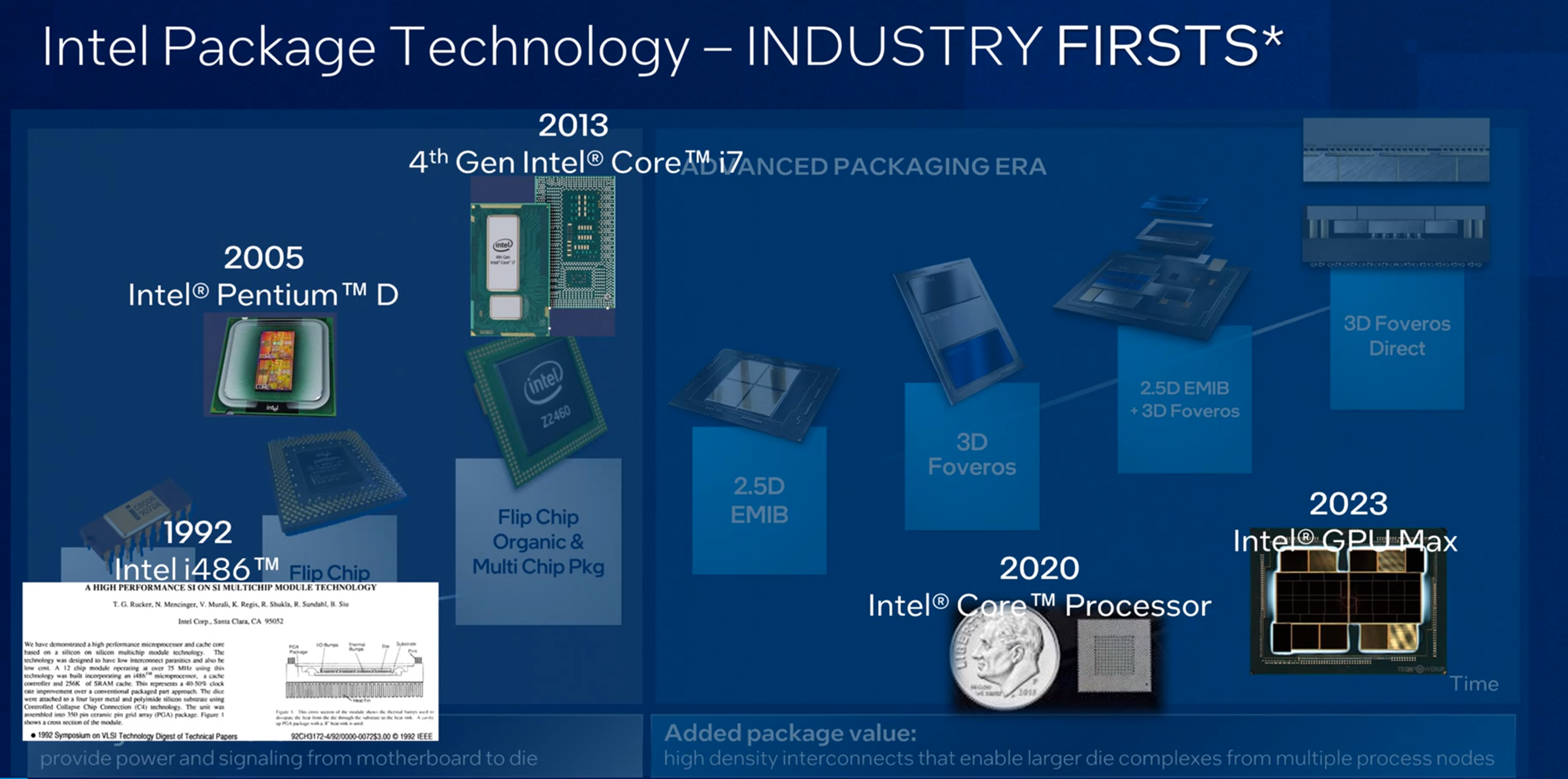

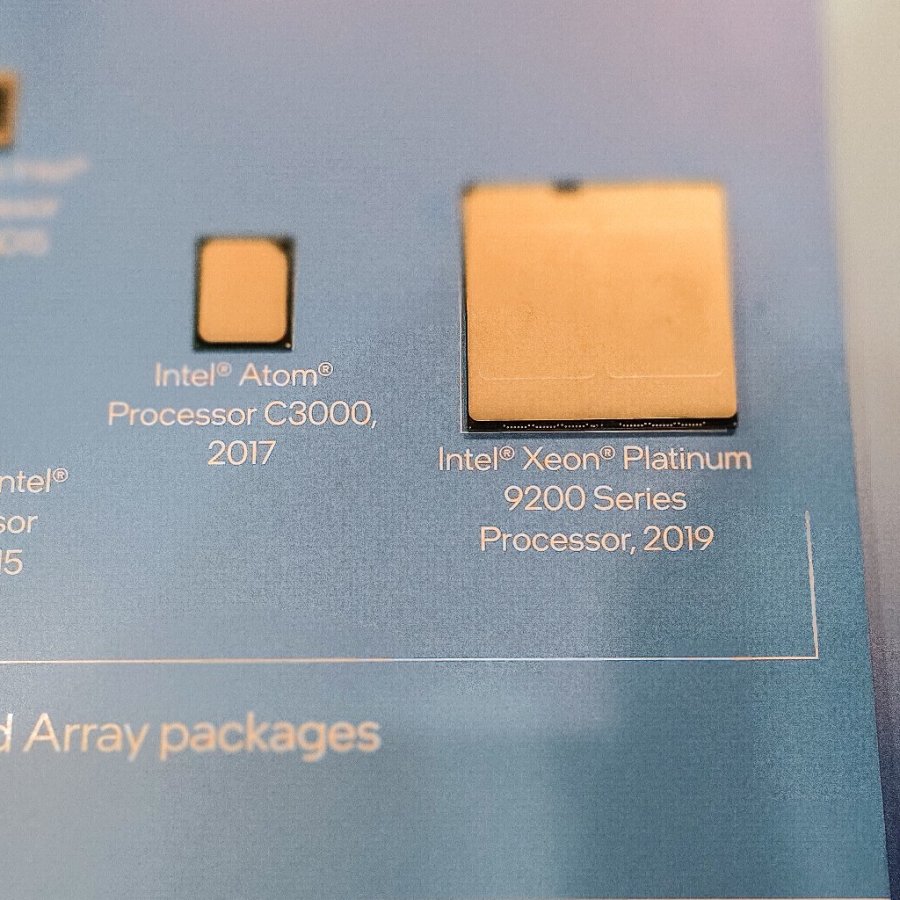

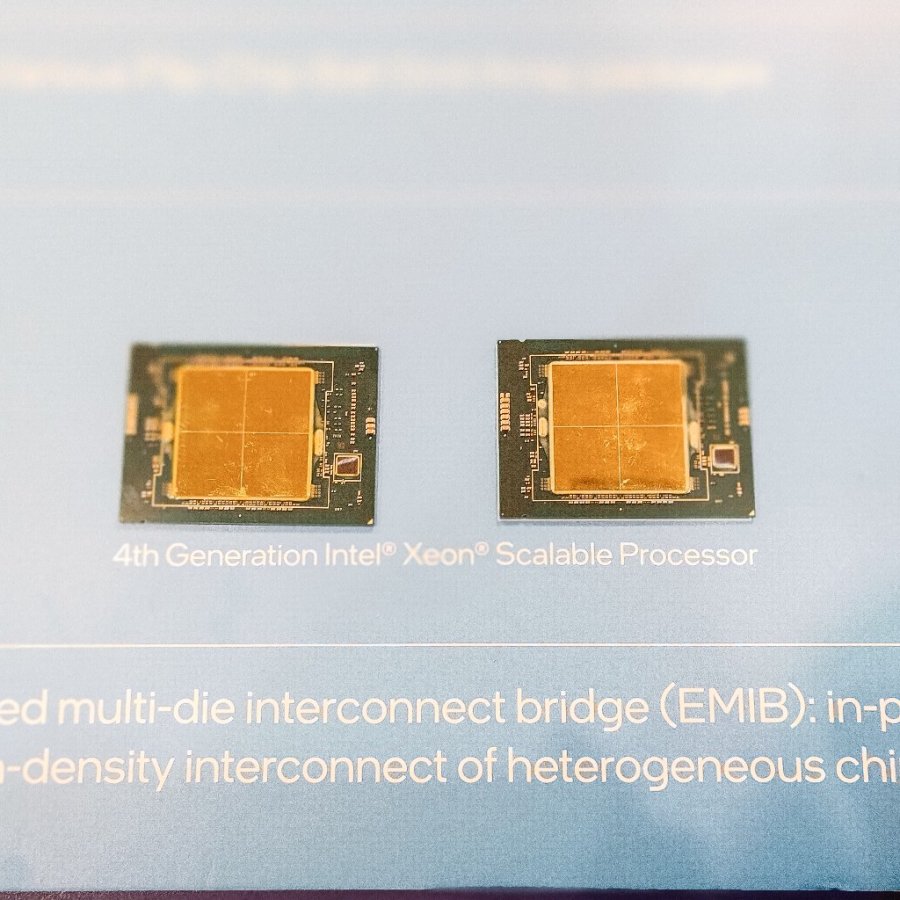

Intel封裝技術的進程

⇧封裝技術減小晶圓尺寸並增加更高密度

3D堆疊晶片是 Intel挑戰 Moore's Law的新方向,它可以將晶片中的邏輯元件堆疊起來,大幅提升 CPU、GPU及 AI處理器的密度,在晶片製程工藝接近停滯的今天,也因為只有這種方法才能繼續提高性能

近日,Intel在半導體行業會議 Hot Chips 34上展示了關於 3D Foveros晶片設計的新細節,它將用於即將發布的 Meteor Lake、Arrow Lake和 Lunar Lake晶片上

當前提供的封裝技術

⇧當前的封裝製程

未來的封裝 Roadmap

Open System Foundry

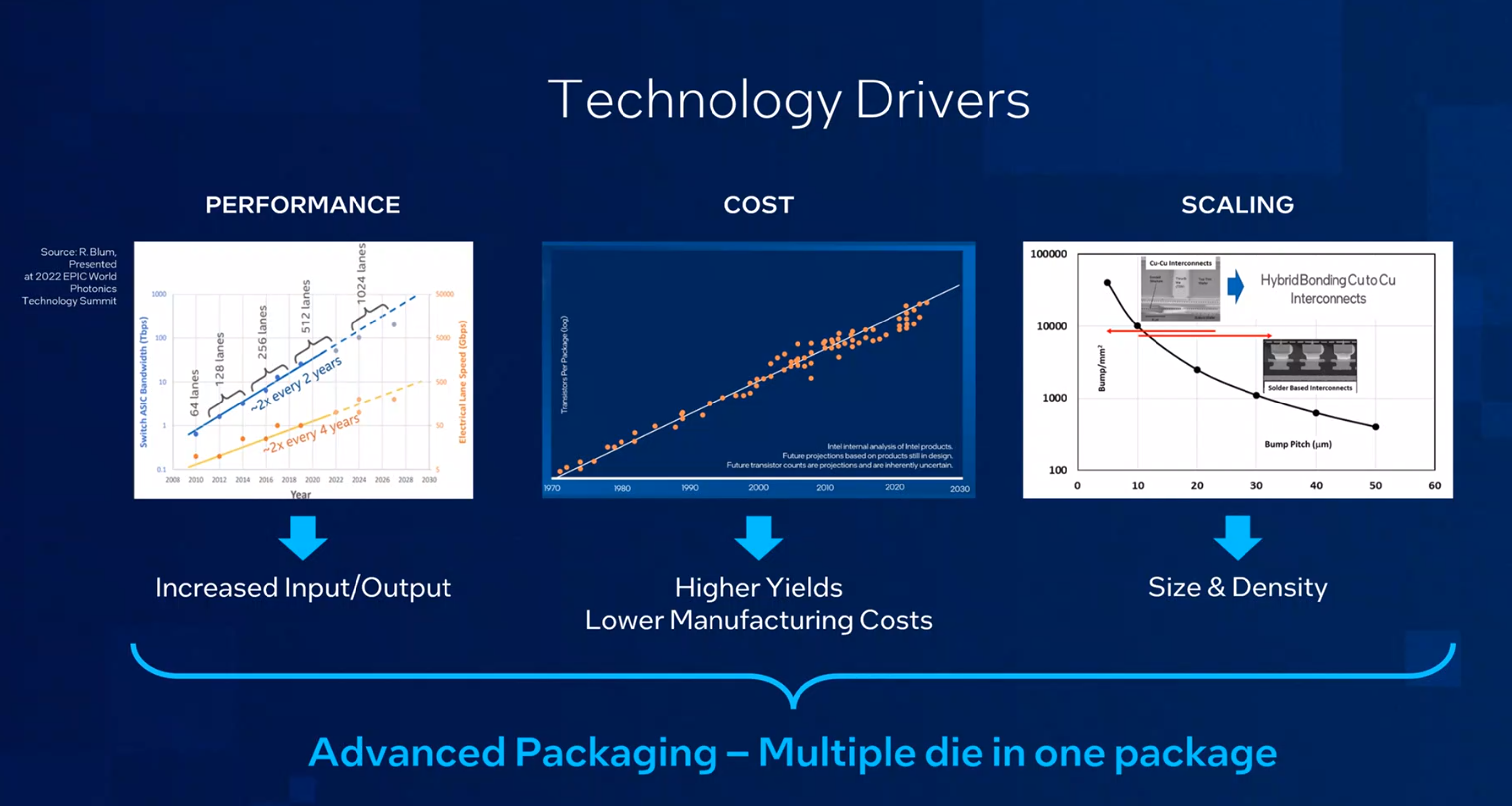

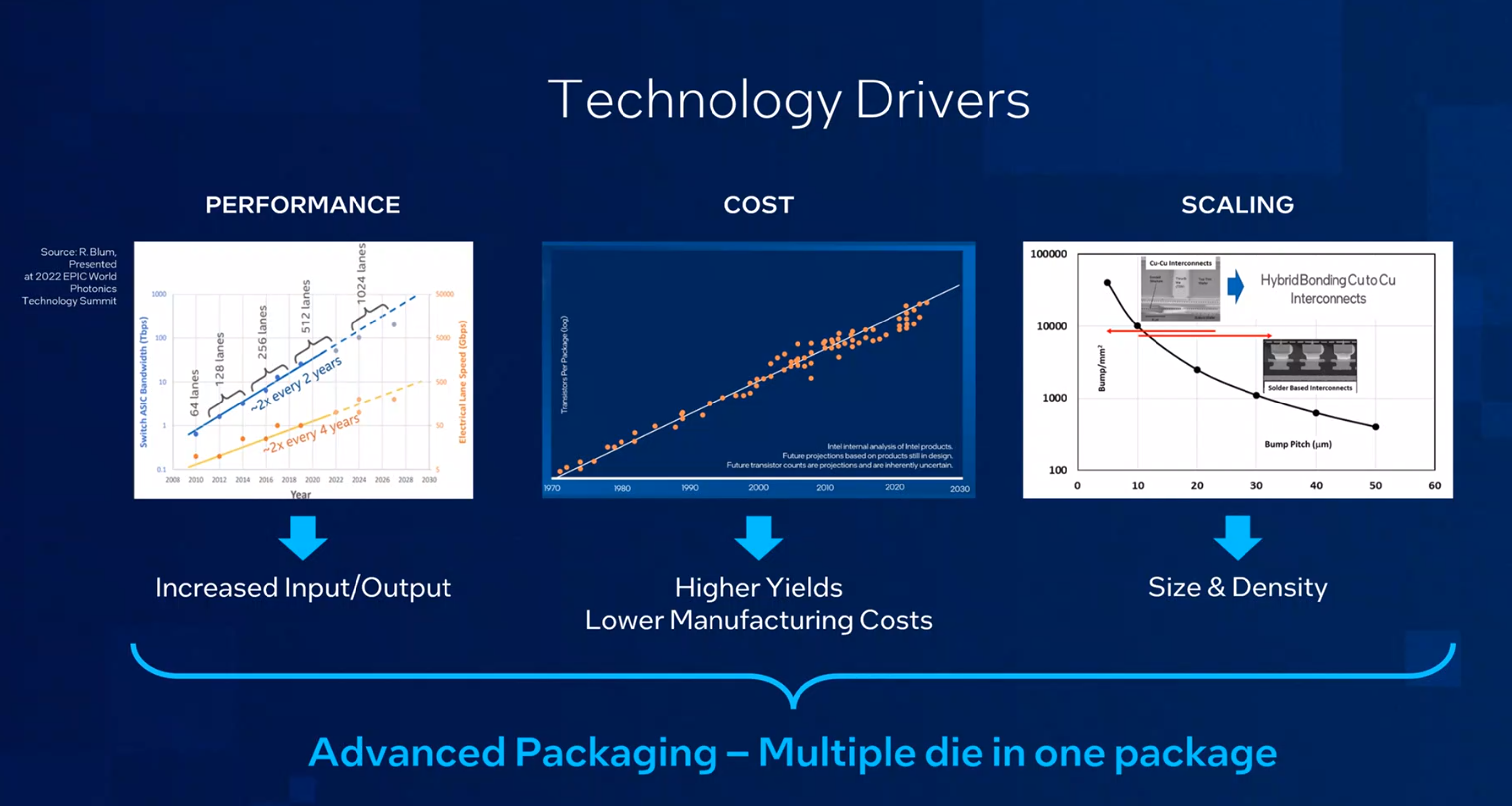

封裝和互連的進步正在迅速改變現代處理器的面貌,兩者現在都與底層工藝節點技術一樣重要

靈活的商業模式

封裝組合測試

Intel先進的封裝技術,採模組化設計 soc使用模組化小晶片可增加良率是一個趨勢也需要推廣,並能提高性能控制成本,以 47個小晶片,9微米 foveros direct為例

⇧IDM 2.0的推廣,封裝代工服務可只做封測部分

堆疊

IDM 2.0代工服務

封裝主張

通過與行業領先專家的一系列精心策劃的討論,詳細了解新技術的創新潛力,以及最小的硬體在這 50年來如何改變世界

Steve Long (亞太區與日本總經理) 的 opening

Intel CEO對晶圓封裝的闡述

參觀封測 Lab

- Intel Validation Lab (Part of megalab)

Intel Validation Lab對CPU、GPU和 FPGA進行各種驗證工作,包括電氣、熱能、功耗、性能等全方面的測試,確保 Intel的產品品質和性能達到標準

- Penang Assembly & Test (PGAT)

Penang Assembly & Test 工廠負責 Intel多條產品線的組裝測試,包括客戶端 CPU、伺服器CPU,以及 GPU等等產品

- Failure Analysis Lab

Failure Analysis Lab負責 Intel CPU的故障分析,透過研究與發現的數據,將結果提供給裝配測試工廠,甚至是晶圓廠,以微調製造過程,降低CPU的故障率

Intel檳城組裝和測試 (PGAT)生產數百萬晶元的大批量生產工廠組裝和測試(PGAT),一個組裝和測試晶元的大批量製造設施,詳情請詳下表

因為在參訪 Lab的過程禁止拍照,所以只能為大家簡單的口述封測及官方提供的照片

晶圓封測(Wafer Packaging and Testing)是半導體製造過程中的一個關鍵步驟,它涉及將製造好的矽晶圓上的多個晶片進行封裝和測試,以製成半導體產品之成品

1. 在晶圓上進行切割,將多個晶片分開,然後將每個晶片封裝到一個獨立的封裝殼體內,並且可以提供保護、散熱和電氣連接功能

2. 連接線和焊點

在封裝過程中,連接線(Wire Bonds)或焊點(Solder Balls)用於連接晶片上的金屬引腳(Bond Pads)與封裝殼體的連接點,這些連接提供了晶片與 ,PCB或 on board之間的電氣連接

3. 測試

在封裝完成後,對每個封裝後的晶片進行功能測試和品質檢查,這包括驗證晶片是否正常運作,以及確保沒有製造缺陷

4. 標識和檢測

在封裝過程中,也會在封裝殼體上添加標籤、條碼或其他識別信息,以便跟蹤和識別不同的封裝晶片

5. 散熱處理

封裝後的晶片可能會產生熱量,因此某些封裝設計還可能包括散熱結構,如散熱片或散熱球,以有效地散熱

6. 功能驗證

在封裝和測試完成後,需要對封裝後的晶片進行最終的功能驗證,確保它們能夠正常運作

整體來說晶圓封測過程就是為確保半導體產品能夠正常運作且品質符合要求的關鍵步驟之一,它將製造好的晶片轉變為最終的成品半導體產品

3D Foveros for meteor Lake

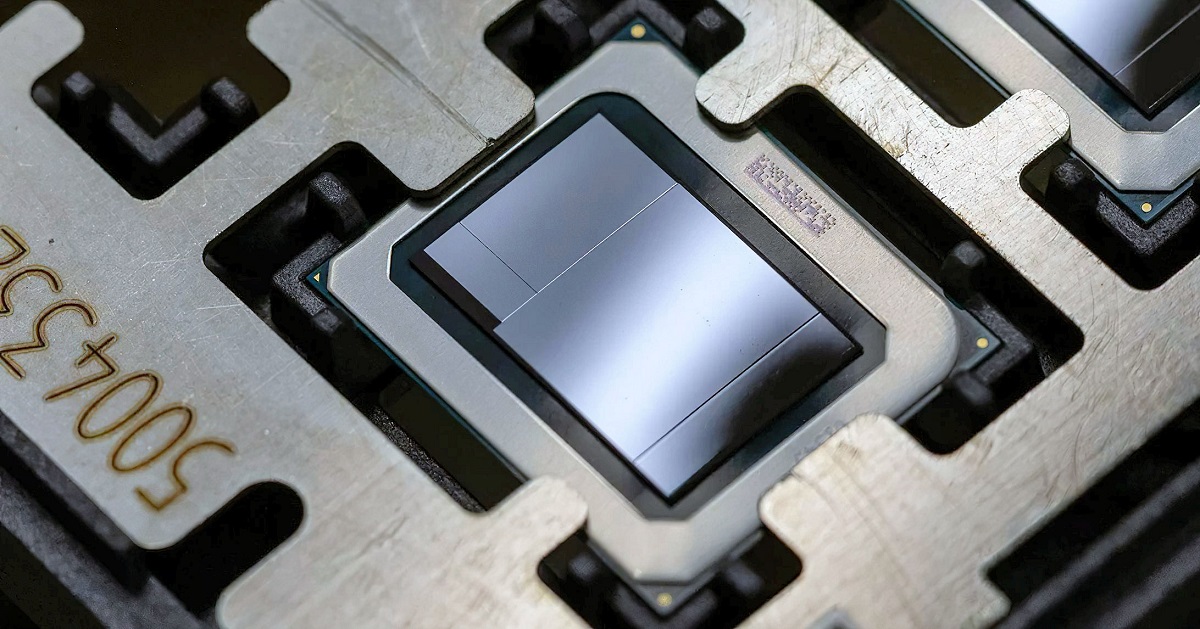

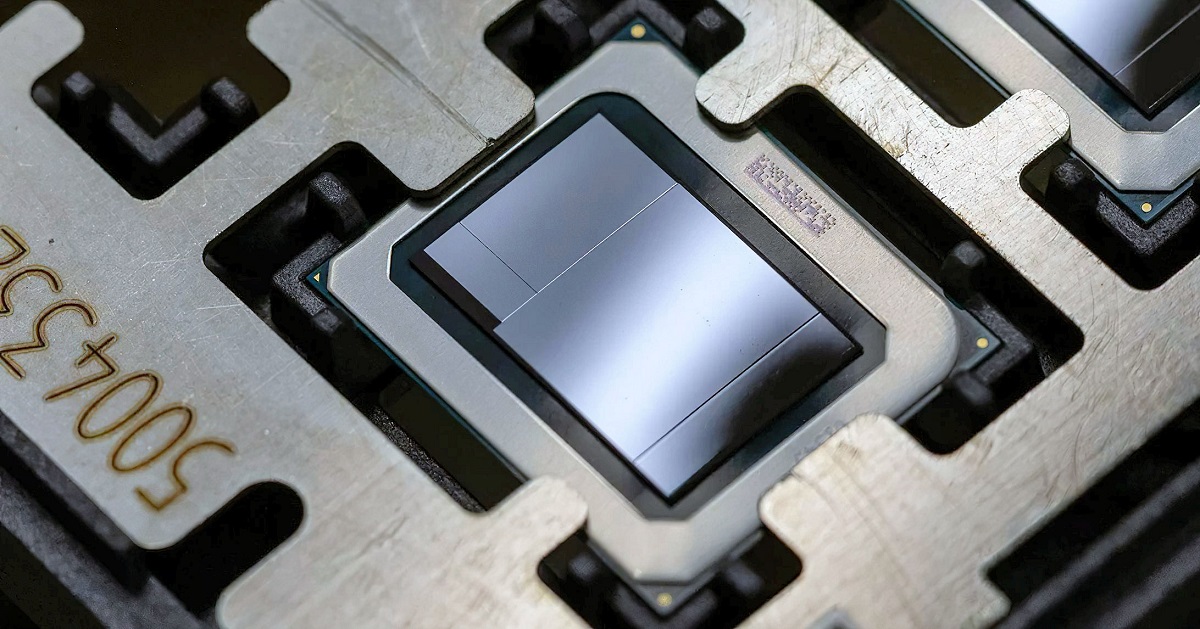

下圖為 Tile chip (進行 3D堆疊前的模樣)

將 Tile chip進行 3D堆疊至 Base Wafer上 (Bond to Bond)

Die Attach

因為晶圓的背面是光滑的亮面,在 Die Attach後的完成面看起來就像是一面反射鏡的 Wafer

Post Mold

「Post Mold」通常是指在 Die Attach之後的工序,以改善產品的外觀、功能或其他特性

這個過程會因產品類型而異,大致上會有以下的步驟

1. 除模與修整(Demolding and Trimming)

取出成型 Wafer然後進行裁切,以去除邊角多餘的材料

2. 表面處理(Surface Treatment)

進行表面處理以提高外觀,可能包括打磨、拋光、減低厚度等

3. 裝配(Assembly)

通過 SMT將不同的部件組裝在一起

4. 印刷與標記(Printing and Marking)

根據需要,如果是 Desktop CPU則會在 IHS上進行印刷、雷射刻印或貼標籤,以顯示品牌、識別信息或其他信息

5. 檢驗與測試(Inspection and Testing)

在一定的標準下進行質量檢查,包含組裝前的示波器測試、超音波測試、顯微鏡錫球觀察等等,在組裝後並對 Platform進行各類 Benchmark,以確保產品符合規格和標準

6.質量控制(Quality Control)

在整個過程中,需要執行質量控制,確保每個步驟都符合標準,確保最終產品的品質是穩定的

7. 包裝(Packaging)

將產品包裝成最終形式,以便運輸、儲存和銷售,包含產品說明書或保修卡等

PGAT封裝過程

Intel Kulim Die sort Die Prep (KMDSDP)

最先進的矽晶圓加工設施

2023年 8月 22日 — 在 Intel居林模具分類模具準備(KMDSP)

這家工廠接收製造來自 Intel代工廠和工藝的矽晶圓,並將它們分類成單獨的晶元,準備用於

在檳城組裝和測試(PGAT)等設施進行組裝和測試

KMDSDP概述

模具準備

模具準備通過鐳射和機械切割、研磨和拋光,將各個模具放入托盤中,托盤移動到模具分類

排序

從晶圓上切割晶元後,會對 Die進行功能測試。為了實現這一目標,讓 Die進入 SDX測試儀,這是一種以高並行度為開發的定製解決方案,將 Die安裝在探針卡上,探針卡包含數千根直接接觸的細針

Intel系統集成和製造服務(模擬系統)

獨一無二的內部電路板製造和測試儀集成工廠

2023年 8 月 22日 — 在 Intel技術馬來西亞之旅中,Intel介紹了一家獨一無二的製造工廠,那就是系統集成和製造服務(SIMS),在 Intel設施和實驗室生產期間測試和驗證矽的設備 SIMS工廠負責生產參考平台驗證(RVP)

面向全球 Intel晶圓廠、工廠和實驗室的主機板和測試工具,使用這些工具在 CPU的生產週期中,

高密度燃燒(HDBl)測試儀以及高密度模組化(HMDT)測試儀

該設備由 SIMS設計和製造,可説明 Intel工廠調試的根本,在盡可能短的時間內檢測發生故障的電路,借助這一獨特的工具,Intel提升了老化測試的準確性及速度

SIMS參訪過程

Intel Meteor Lake (以下言論不代表 Intel立場)

Intel Meteor Lake雖然尚未發布,但 Meteor Lake或將使用 Intel 4行程節點(7nm製程)

Meteor Lake擁有六個 「P Core」和二個「E Core」,首要產品將只有筆電處理器

Meteor Lake將使用第二代混合架構技術,P-Core將用 Redwood Cove架構,以取代目前的 Golden Cove架構,E-Core改用 Crestmont架構,替換 Gracemont 。其採用了 Tile設計,會有四個不同的模組,分別是計算模組、SOC 模組、I/O模組和 GPU模組,這些模組可以採用不同製程製造,然後進行堆疊,再使用 EMIB技術互聯和 Foveros封裝技術

而 2024的 Arrow Lake晶片則將覆蓋到 Desktop,之後的 Lunar Lake則將用於功率小於等於 15W的輕薄筆電

Intel Meteor Lake晶片示意圖

⇧把 4個 Meteor Lake小晶片「tile」放置在 Foveros仲介層 / 基礎 tile的頂部,小晶片和仲介層透過 TSV連接連在一起,3D Foveros 封裝技術還支援有源仲介層,Intel使用低成本和低功耗最佳化的 22FFL工藝(與 Lakefield 相同)製造 Foveros仲介層,並把 3D Foveros 推向市場,在 4 tile的 Meteor Lake 和 47 tile 的 Ponte Vecchio之後,Intel將過渡到新的 UCIe互連,進而進入使用標準化介面的小晶片(chiplet)生態系統

Arrow Lake-S(Z890、B860 & H810 MOBO)

⇧2024年的 Arrow Lake-S最高可能一樣維持 8大核心加上 16小核心,最多 24核 32執行緒,不過大核心 L2 Cache配置將會增加到每核心 3MB,而且 Xe2 內顯將會有專用的 L3 Cache,另外在命名上面部分會有所改變,如原本 Core i7變成 Core Ultra 7

結語:

Intel的組裝測試遍佈於全球各地,即將於 2024年啟用的 Intel Penang廠未來會將會承續奧勒岡與新墨西哥場之 3D Advance & Foveros封裝技術,並用在 Meteo Lake & Allow Lake上,雖然 Moore (Intel創辦人之一) 在今年三月以 94歲高齡過世,但 Moore‘s Law並未因此而停滯,Intel仍然繼續挑戰 Moore's Law的新方向,那就是繼續進行更先進的 3D堆疊,3D堆疊它可以將晶片中的邏輯元件堆疊起來,來大幅提升 CPU、GPU及 AI處理器的密度,在晶片製程工藝接近停滯的今天,把小晶片垂直堆疊在一個具有 Foveros互連的統一基礎晶片上,也只有 Intel的先進科技的這種方法才能繼續提高性能;Intel還將 Foveros用於其 Ponte Vecchio和 Rialto Bridge GPU以及 Agilex FPGA (新墨西哥廠),因此它可視為該公司若干下代產品的基礎技術,並透過垂直整合製造模式推廣 IDM 2.0之代工服務

Intel長年在馬來西亞深耕晶圓封測,更於 2021年 12月時在馬來西亞投資約 71億美元的擴充計畫,這項投資旨在增強其在該地區的半導體製造和封裝測試能力,以應對不斷增長的需求並提升其在全球市場的競爭力,擴增的晶圓廠除了一般封裝測試的產線之外也會針對 Meteor Lake & Allow Lake (LGA1851)的 3D Foveros封裝;封裝測試是指將製造好的晶圓封裝在保護外殼內,以確保其在實際應用中的保護和運作,而半導體測試則是確保每個晶片都能正常運作並符合品質標準,這些封裝和測試工作是半導體製造過程中不可或缺的一部分,有助於確保最終產品的穩定性和可靠性;通常,這些工作也是半導體製造供應鏈中的重要環節之一,以確保製品能夠達到預期的性能和品質

滄者有幸也參加了 Intel 51年來首次開放媒體參訪的 Intel Technology Tour 2023 for 3D Advance ,Intel Technology Tour 2023活動聚焦在 Intel致力於創新策略與製造領域的領導地位,帶領全球媒體參訪 Intel位在馬來西亞的半導體封裝測試廠,並分享公司轉型策略「垂直整合製造模式 IDM 2.0」、最新技術發展,以及現場直擊即將發布的 Meteor Lake處理器的技術細節

Intel Penang封測廠

整個區域到處都是 Intel building,包含正在興建中並會在 2024啟用的封測廠房 (未來它將用於即將發布的 Meteor Lake、Arrow Lake和 Lunar Lake晶片上)

而在 Lab廠房到處都佈置有 Intel TECH Tour的 POP

參訪人員魚貫進場

途經 Crew的辦公室場景

參訪人群先安排到簡報室聽取簡報

參訪前的簡報

在介紹本次參訪的過程之前讓我們先來看看 Intel的 3D封裝測試技術的介紹

開場

概觀

眾所皆知的依照 Intel Moore's Law,在當下一個 Chiplet可以容納 1千億個晶體管,而當電腦晶片正式進入 3D時代時,在 2030年時一個 Chiplet則將能容納有一萬億個電晶體

4年 5節點的 Moore's Law摩爾定律

Steven Long提到 intel轉型的三大要素,第一點就是 Advancing Moore's Law,以 5N4D為主要目標

除了透過製程在同樣面積塞入更多電晶體之外,另一方面也透過先進封裝技術,在同樣的面積上透過 3D堆疊增加更多的運算能力,Moore在很久之前就有說過這樣的概念: 「It may prove to be more economical to build large systems out of smaller functions, which are separately packagedand interconnecte」

多重 Die的先進 3D封裝

Intel封裝技術的進程

⇧封裝技術減小晶圓尺寸並增加更高密度

3D堆疊晶片是 Intel挑戰 Moore's Law的新方向,它可以將晶片中的邏輯元件堆疊起來,大幅提升 CPU、GPU及 AI處理器的密度,在晶片製程工藝接近停滯的今天,也因為只有這種方法才能繼續提高性能

近日,Intel在半導體行業會議 Hot Chips 34上展示了關於 3D Foveros晶片設計的新細節,它將用於即將發布的 Meteor Lake、Arrow Lake和 Lunar Lake晶片上

當前提供的封裝技術

⇧當前的封裝製程

未來的封裝 Roadmap

Open System Foundry

封裝和互連的進步正在迅速改變現代處理器的面貌,兩者現在都與底層工藝節點技術一樣重要

靈活的商業模式

封裝組合測試

Intel先進的封裝技術,採模組化設計 soc使用模組化小晶片可增加良率是一個趨勢也需要推廣,並能提高性能控制成本,以 47個小晶片,9微米 foveros direct為例

⇧IDM 2.0的推廣,封裝代工服務可只做封測部分

堆疊

IDM 2.0代工服務

封裝主張

通過與行業領先專家的一系列精心策劃的討論,詳細了解新技術的創新潛力,以及最小的硬體在這 50年來如何改變世界

Steve Long (亞太區與日本總經理) 的 opening

Intel CEO對晶圓封裝的闡述

參觀封測 Lab

- Intel Validation Lab (Part of megalab)

Intel Validation Lab對CPU、GPU和 FPGA進行各種驗證工作,包括電氣、熱能、功耗、性能等全方面的測試,確保 Intel的產品品質和性能達到標準

- Penang Assembly & Test (PGAT)

Penang Assembly & Test 工廠負責 Intel多條產品線的組裝測試,包括客戶端 CPU、伺服器CPU,以及 GPU等等產品

- Failure Analysis Lab

Failure Analysis Lab負責 Intel CPU的故障分析,透過研究與發現的數據,將結果提供給裝配測試工廠,甚至是晶圓廠,以微調製造過程,降低CPU的故障率

Intel檳城組裝和測試 (PGAT)生產數百萬晶元的大批量生產工廠組裝和測試(PGAT),一個組裝和測試晶元的大批量製造設施,詳情請詳下表

因為在參訪 Lab的過程禁止拍照,所以只能為大家簡單的口述封測及官方提供的照片

晶圓封測(Wafer Packaging and Testing)是半導體製造過程中的一個關鍵步驟,它涉及將製造好的矽晶圓上的多個晶片進行封裝和測試,以製成半導體產品之成品

1. 在晶圓上進行切割,將多個晶片分開,然後將每個晶片封裝到一個獨立的封裝殼體內,並且可以提供保護、散熱和電氣連接功能

2. 連接線和焊點

在封裝過程中,連接線(Wire Bonds)或焊點(Solder Balls)用於連接晶片上的金屬引腳(Bond Pads)與封裝殼體的連接點,這些連接提供了晶片與 ,PCB或 on board之間的電氣連接

3. 測試

在封裝完成後,對每個封裝後的晶片進行功能測試和品質檢查,這包括驗證晶片是否正常運作,以及確保沒有製造缺陷

4. 標識和檢測

在封裝過程中,也會在封裝殼體上添加標籤、條碼或其他識別信息,以便跟蹤和識別不同的封裝晶片

5. 散熱處理

封裝後的晶片可能會產生熱量,因此某些封裝設計還可能包括散熱結構,如散熱片或散熱球,以有效地散熱

6. 功能驗證

在封裝和測試完成後,需要對封裝後的晶片進行最終的功能驗證,確保它們能夠正常運作

整體來說晶圓封測過程就是為確保半導體產品能夠正常運作且品質符合要求的關鍵步驟之一,它將製造好的晶片轉變為最終的成品半導體產品

3D Foveros for meteor Lake

下圖為 Tile chip (進行 3D堆疊前的模樣)

將 Tile chip進行 3D堆疊至 Base Wafer上 (Bond to Bond)

Die Attach

因為晶圓的背面是光滑的亮面,在 Die Attach後的完成面看起來就像是一面反射鏡的 Wafer

Post Mold

「Post Mold」通常是指在 Die Attach之後的工序,以改善產品的外觀、功能或其他特性

這個過程會因產品類型而異,大致上會有以下的步驟

1. 除模與修整(Demolding and Trimming)

取出成型 Wafer然後進行裁切,以去除邊角多餘的材料

2. 表面處理(Surface Treatment)

進行表面處理以提高外觀,可能包括打磨、拋光、減低厚度等

3. 裝配(Assembly)

通過 SMT將不同的部件組裝在一起

4. 印刷與標記(Printing and Marking)

根據需要,如果是 Desktop CPU則會在 IHS上進行印刷、雷射刻印或貼標籤,以顯示品牌、識別信息或其他信息

5. 檢驗與測試(Inspection and Testing)

在一定的標準下進行質量檢查,包含組裝前的示波器測試、超音波測試、顯微鏡錫球觀察等等,在組裝後並對 Platform進行各類 Benchmark,以確保產品符合規格和標準

6.質量控制(Quality Control)

在整個過程中,需要執行質量控制,確保每個步驟都符合標準,確保最終產品的品質是穩定的

7. 包裝(Packaging)

將產品包裝成最終形式,以便運輸、儲存和銷售,包含產品說明書或保修卡等

PGAT封裝過程

Intel Kulim Die sort Die Prep (KMDSDP)

最先進的矽晶圓加工設施

2023年 8月 22日 — 在 Intel居林模具分類模具準備(KMDSP)

這家工廠接收製造來自 Intel代工廠和工藝的矽晶圓,並將它們分類成單獨的晶元,準備用於

在檳城組裝和測試(PGAT)等設施進行組裝和測試

KMDSDP概述

模具準備

模具準備通過鐳射和機械切割、研磨和拋光,將各個模具放入托盤中,托盤移動到模具分類

排序

從晶圓上切割晶元後,會對 Die進行功能測試。為了實現這一目標,讓 Die進入 SDX測試儀,這是一種以高並行度為開發的定製解決方案,將 Die安裝在探針卡上,探針卡包含數千根直接接觸的細針

Intel系統集成和製造服務(模擬系統)

獨一無二的內部電路板製造和測試儀集成工廠

2023年 8 月 22日 — 在 Intel技術馬來西亞之旅中,Intel介紹了一家獨一無二的製造工廠,那就是系統集成和製造服務(SIMS),在 Intel設施和實驗室生產期間測試和驗證矽的設備 SIMS工廠負責生產參考平台驗證(RVP)

面向全球 Intel晶圓廠、工廠和實驗室的主機板和測試工具,使用這些工具在 CPU的生產週期中,

高密度燃燒(HDBl)測試儀以及高密度模組化(HMDT)測試儀

該設備由 SIMS設計和製造,可説明 Intel工廠調試的根本,在盡可能短的時間內檢測發生故障的電路,借助這一獨特的工具,Intel提升了老化測試的準確性及速度

SIMS參訪過程

Intel Meteor Lake (以下言論不代表 Intel立場)

Intel Meteor Lake雖然尚未發布,但 Meteor Lake或將使用 Intel 4行程節點(7nm製程)

Meteor Lake擁有六個 「P Core」和二個「E Core」,首要產品將只有筆電處理器

Meteor Lake將使用第二代混合架構技術,P-Core將用 Redwood Cove架構,以取代目前的 Golden Cove架構,E-Core改用 Crestmont架構,替換 Gracemont 。其採用了 Tile設計,會有四個不同的模組,分別是計算模組、SOC 模組、I/O模組和 GPU模組,這些模組可以採用不同製程製造,然後進行堆疊,再使用 EMIB技術互聯和 Foveros封裝技術

而 2024的 Arrow Lake晶片則將覆蓋到 Desktop,之後的 Lunar Lake則將用於功率小於等於 15W的輕薄筆電

Intel Meteor Lake晶片示意圖

⇧把 4個 Meteor Lake小晶片「tile」放置在 Foveros仲介層 / 基礎 tile的頂部,小晶片和仲介層透過 TSV連接連在一起,3D Foveros 封裝技術還支援有源仲介層,Intel使用低成本和低功耗最佳化的 22FFL工藝(與 Lakefield 相同)製造 Foveros仲介層,並把 3D Foveros 推向市場,在 4 tile的 Meteor Lake 和 47 tile 的 Ponte Vecchio之後,Intel將過渡到新的 UCIe互連,進而進入使用標準化介面的小晶片(chiplet)生態系統

Arrow Lake-S(Z890、B860 & H810 MOBO)

⇧2024年的 Arrow Lake-S最高可能一樣維持 8大核心加上 16小核心,最多 24核 32執行緒,不過大核心 L2 Cache配置將會增加到每核心 3MB,而且 Xe2 內顯將會有專用的 L3 Cache,另外在命名上面部分會有所改變,如原本 Core i7變成 Core Ultra 7

結語:

Intel的組裝測試遍佈於全球各地,即將於 2024年啟用的 Intel Penang廠未來會將會承續奧勒岡與新墨西哥場之 3D Advance & Foveros封裝技術,並用在 Meteo Lake & Allow Lake上,雖然 Moore (Intel創辦人之一) 在今年三月以 94歲高齡過世,但 Moore‘s Law並未因此而停滯,Intel仍然繼續挑戰 Moore's Law的新方向,那就是繼續進行更先進的 3D堆疊,3D堆疊它可以將晶片中的邏輯元件堆疊起來,來大幅提升 CPU、GPU及 AI處理器的密度,在晶片製程工藝接近停滯的今天,把小晶片垂直堆疊在一個具有 Foveros互連的統一基礎晶片上,也只有 Intel的先進科技的這種方法才能繼續提高性能;Intel還將 Foveros用於其 Ponte Vecchio和 Rialto Bridge GPU以及 Agilex FPGA (新墨西哥廠),因此它可視為該公司若干下代產品的基礎技術,並透過垂直整合製造模式推廣 IDM 2.0之代工服務

附件

-

PSX_20230821_102330_copy_1024x627.jpg188.4 KB · 人氣: 88

PSX_20230821_102330_copy_1024x627.jpg188.4 KB · 人氣: 88 -

PSX_20230821_102422_copy_1024x641.jpg215.2 KB · 人氣: 54

PSX_20230821_102422_copy_1024x641.jpg215.2 KB · 人氣: 54 -

PSX_20230821_133920_copy_1024x860.jpg916.3 KB · 人氣: 57

PSX_20230821_133920_copy_1024x860.jpg916.3 KB · 人氣: 57 -

PSX_20230821_134601_copy_1024x1024.jpg332.5 KB · 人氣: 54

PSX_20230821_134601_copy_1024x1024.jpg332.5 KB · 人氣: 54 -

PSX_20230821_134623_copy_1024x1024.jpg258 KB · 人氣: 43

PSX_20230821_134623_copy_1024x1024.jpg258 KB · 人氣: 43 -

PSX_20230821_210512.png416.5 KB · 人氣: 48

PSX_20230821_210512.png416.5 KB · 人氣: 48