Intel 近日釋出了 Alder Lake 開發人員指南,在上面公開了一些之前沒有釋出的相關資訊,包括大致的 SKU 以及指令集支援情況,因為 Alder Lake 是由 Golden Cove (P-Core)和 Gracemont (E-Core) 兩種不同架構的核心所組成的,所以它與以往的處理器相比會有更多不同的核心組合。

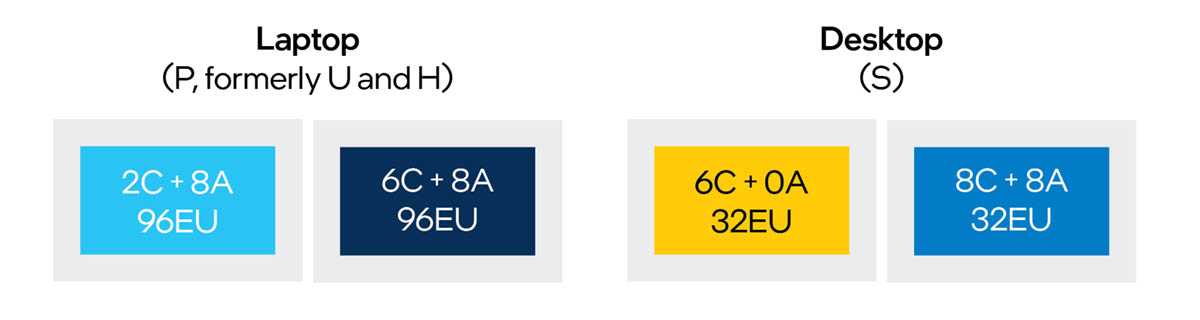

桌面版的核心代號為 Alder Lake-S,旗艦核心是有8個 P-Core 加8個 E-Core 組成,配備32組 EU 的內顯,而另一種核心則只有6個 P-Core,內顯均是最多32組 EU,根據此前的消息,Core i5-12600K 及更高的型號都會用上大小核心混合,而 Core i5-12600 及以下的型號都是用只有 P-Core 大核心。

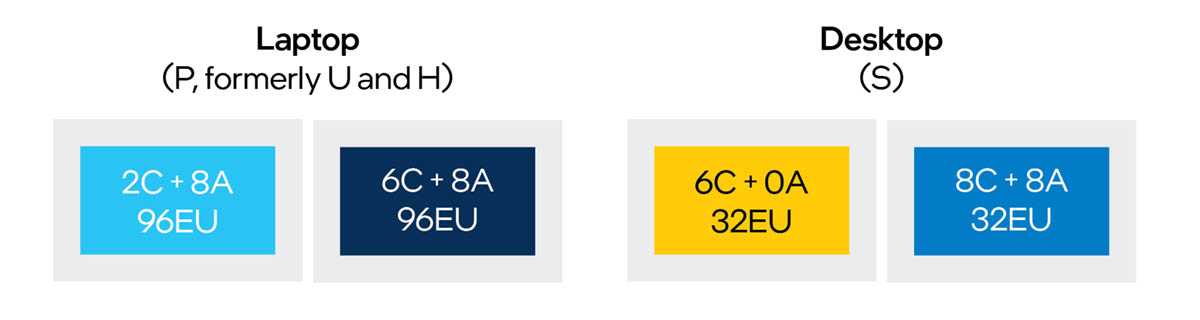

移動版改變了以前用 U 與 H 的核心分類,統一叫 Alder Lake-P,但具體的處理器型號還是會分 U 和 H,與桌面版不同,移動版的 Alder Lake-P 全部都有 E-Core 小核心,取代 Tiger Lake-U 的 Alder Lake-P 有2個 P-Core 和8個 E-Core,而取代 Tiger Lake-H 的則最多有6個 P-Core 和8個 E-Core,內顯則是最多96組 EU。

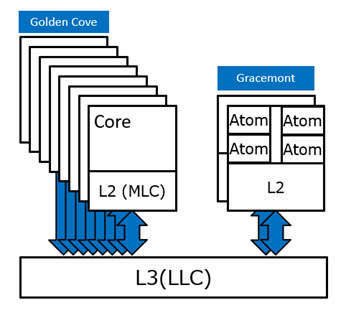

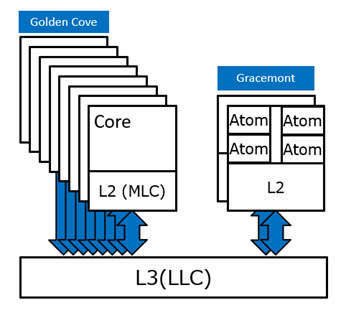

根據 Intel 給出的示意圖,每個 P-Core 都是有自己的 L2 快取,並且是直接與 L3 快取相連的,而 E-Core 則是4個一組,共用 L2 並與 L3 相連。

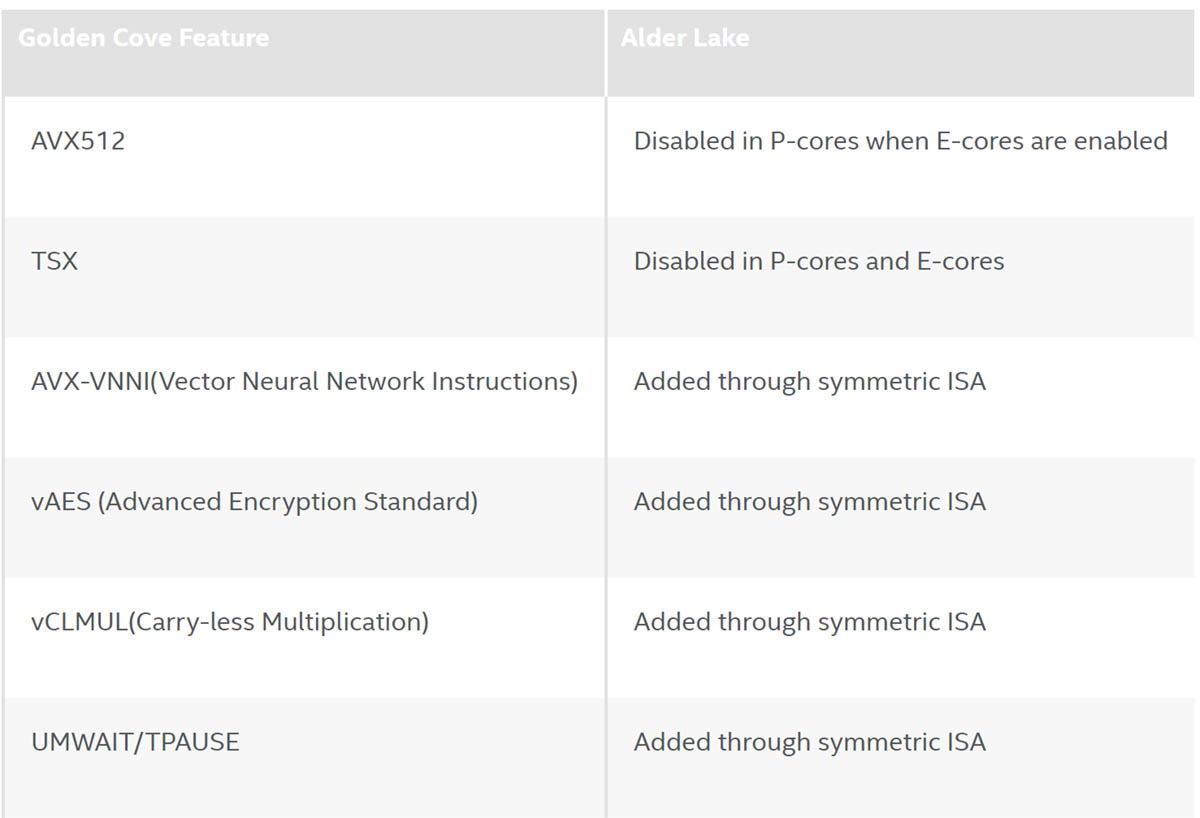

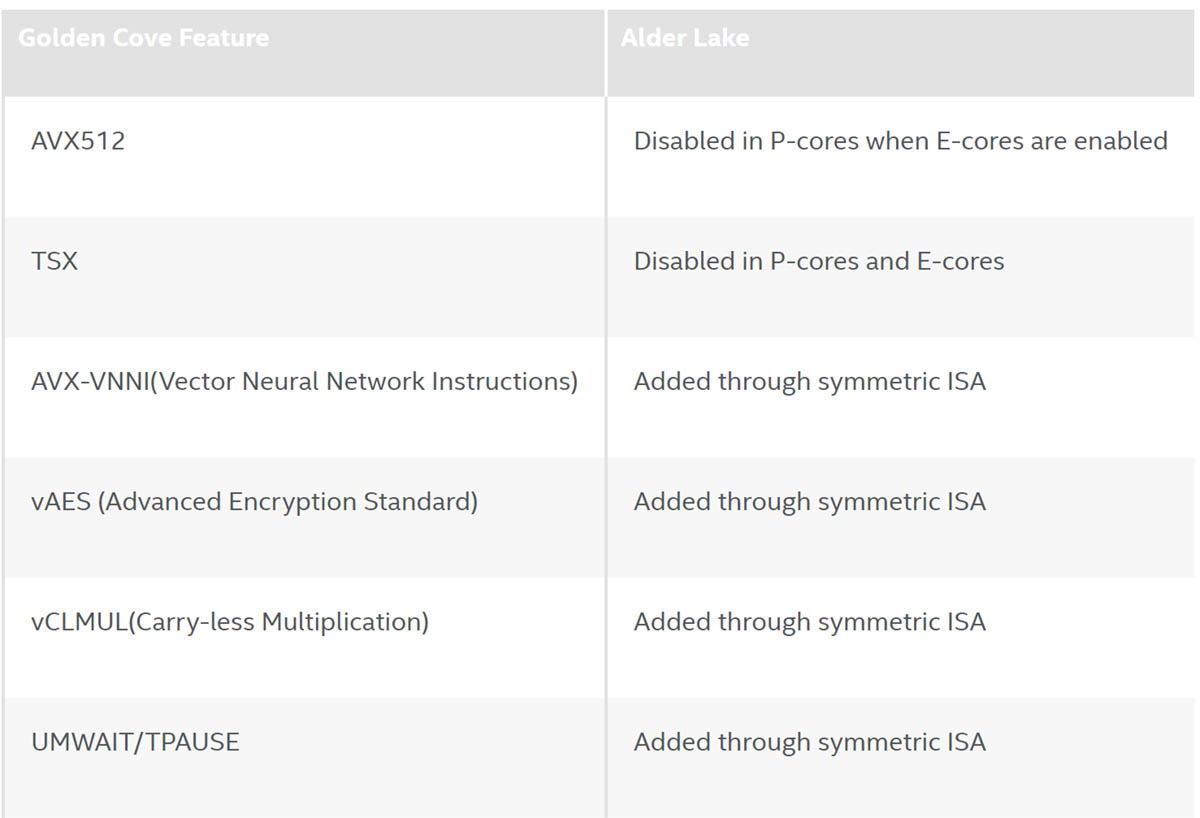

關於指令集方面,Golden Cove 是支援 AVX512,但 Gracemont 小核心不支援,所以目前 Intel 給出的解決方案就是當 E-Core 啟用時 AVX512 就會被禁用,而 AVX512 的開關是否給出就可由 OEM 廠商來決定。 TSX 指令集則是直接被禁用,其他的 AVX-VNNI、vAES、vCLMUL 和 UMWAIT / TPAUSE 則是可由 ISA 添加。

來源

桌面版的核心代號為 Alder Lake-S,旗艦核心是有8個 P-Core 加8個 E-Core 組成,配備32組 EU 的內顯,而另一種核心則只有6個 P-Core,內顯均是最多32組 EU,根據此前的消息,Core i5-12600K 及更高的型號都會用上大小核心混合,而 Core i5-12600 及以下的型號都是用只有 P-Core 大核心。

移動版改變了以前用 U 與 H 的核心分類,統一叫 Alder Lake-P,但具體的處理器型號還是會分 U 和 H,與桌面版不同,移動版的 Alder Lake-P 全部都有 E-Core 小核心,取代 Tiger Lake-U 的 Alder Lake-P 有2個 P-Core 和8個 E-Core,而取代 Tiger Lake-H 的則最多有6個 P-Core 和8個 E-Core,內顯則是最多96組 EU。

根據 Intel 給出的示意圖,每個 P-Core 都是有自己的 L2 快取,並且是直接與 L3 快取相連的,而 E-Core 則是4個一組,共用 L2 並與 L3 相連。

關於指令集方面,Golden Cove 是支援 AVX512,但 Gracemont 小核心不支援,所以目前 Intel 給出的解決方案就是當 E-Core 啟用時 AVX512 就會被禁用,而 AVX512 的開關是否給出就可由 OEM 廠商來決定。 TSX 指令集則是直接被禁用,其他的 AVX-VNNI、vAES、vCLMUL 和 UMWAIT / TPAUSE 則是可由 ISA 添加。

來源