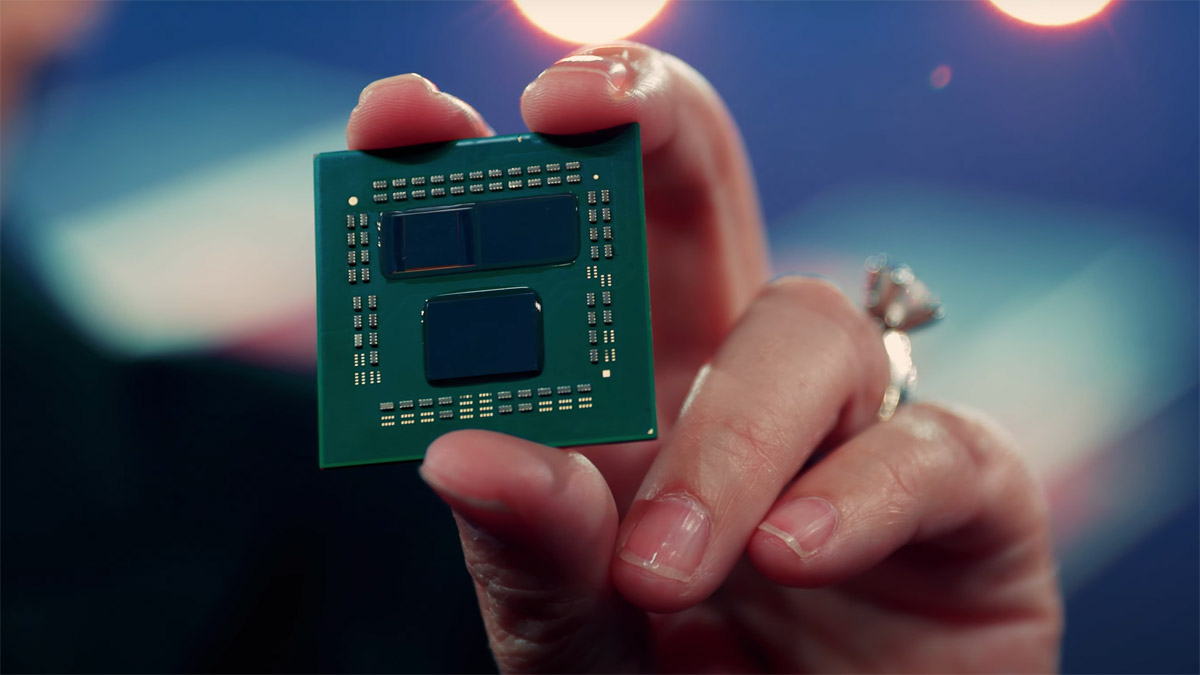

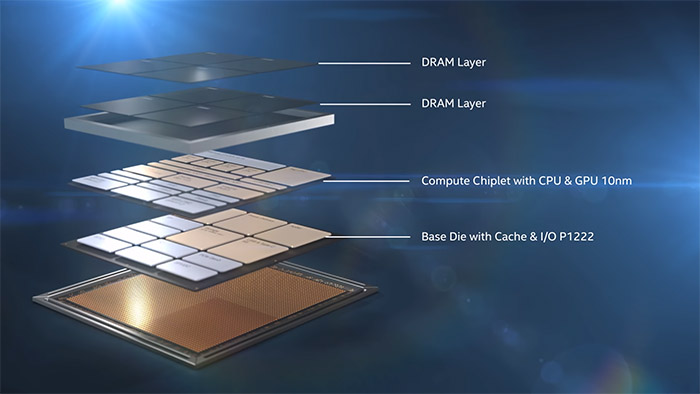

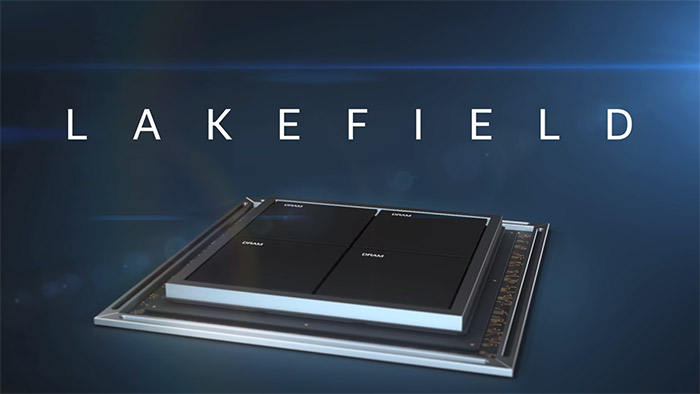

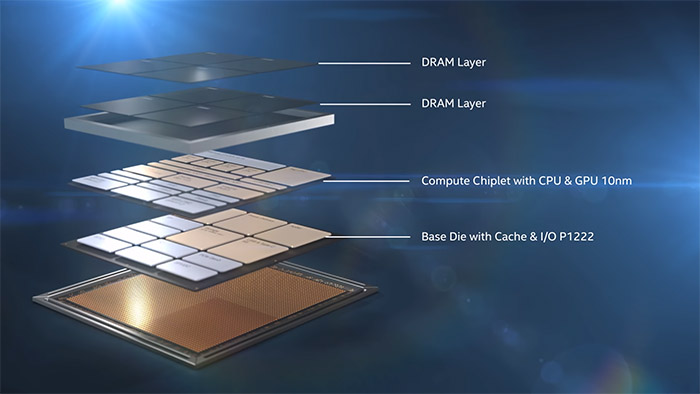

最近 Intel 在 Youtube 上放出了採用 Foveros 3D 封裝製程所生產的 Lakefield SoC 的介紹影片,從影片可以看出這個 SoC 至少包含四個層,前兩層是由 PoP 封裝的 DRAM 所組成,由兩塊 BGA DRAM 堆疊在一起,第三層則是由10nm製程打造的 CPU 與 GPU,最底層則是由22nm製程打造的I/O與快取層。

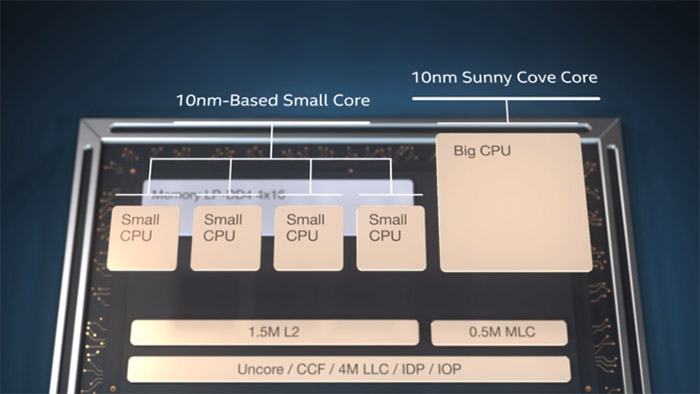

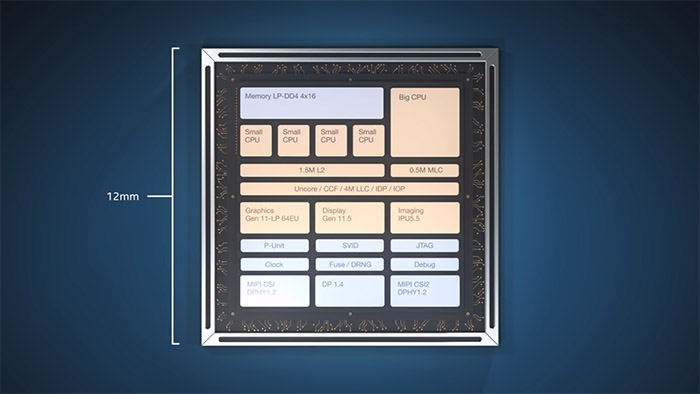

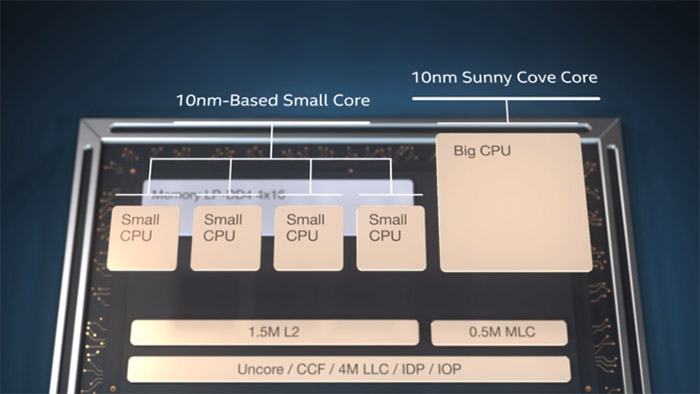

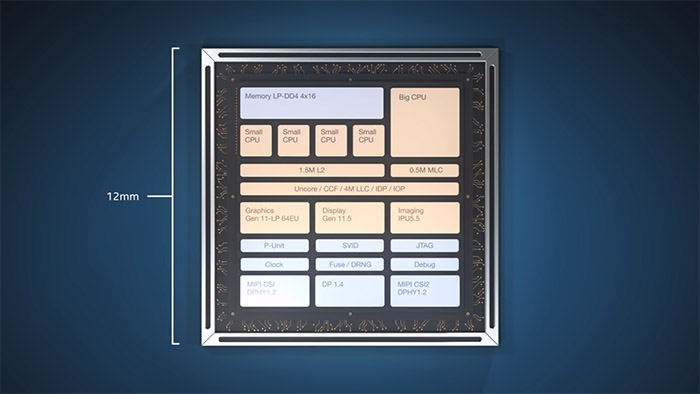

10nm製程的計算晶片包含一個 Sunny Cove 大核,該核心擁有自己的L2快取,不過它核心外還有0.5MB的 MLC 中等級快取,四個 Tremont 小核,它們共享1.5M L2快取,所有核心共享4MB的 LLC 快取,記憶體控制器是4*16位的,支援 LPDDR4,整合了 Gen 11 內顯,有64個EU單元,Gen 11.5 的顯示控制器還有新的 IPU,並且支援 DP 1.4。

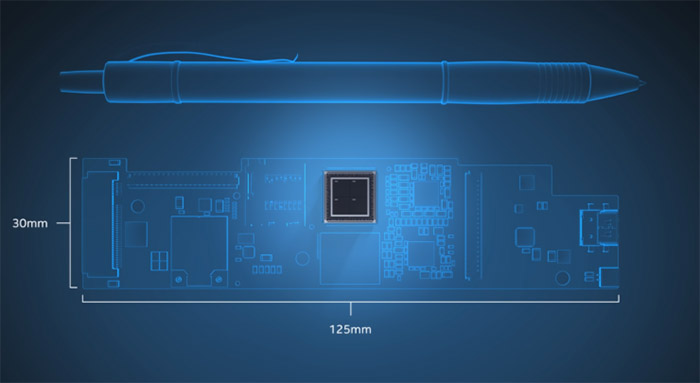

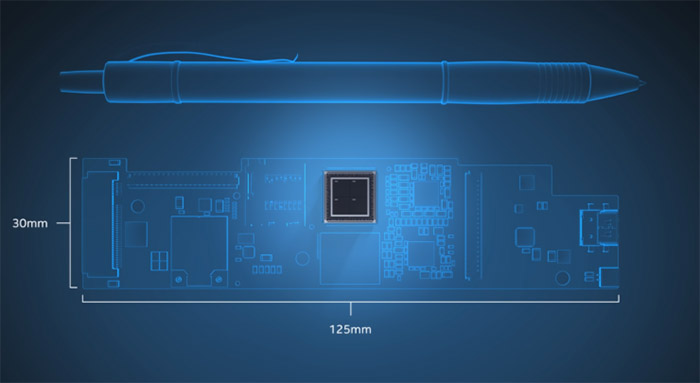

位於底部的基底層作為 SoC 的快取與 I/O 模組,應該整合了 PCI-E 控制器並擁有 PCH 晶片的部分功能,為 SoC 提供豐富的 I/O 功能,由於 SoC 直接整合了記憶體模塊,所以可以讓移動設備的主板變得更為小巧,而 Lakefield SoC 本身也只有12*12mm那麼大,TDP 不會高於7W,它的出現可以讓未來的移動設備變得更輕薄,並且有更強的續航能力。

但是目前還不知道這個 Lakefield SoC 是否需要搭配 PCH 所使用,因為從上圖來看 SoC 下面那個大晶片看起來像是 PCH,不過目前無法確定。

來源:https://www.expreview.com/67009.html

10nm製程的計算晶片包含一個 Sunny Cove 大核,該核心擁有自己的L2快取,不過它核心外還有0.5MB的 MLC 中等級快取,四個 Tremont 小核,它們共享1.5M L2快取,所有核心共享4MB的 LLC 快取,記憶體控制器是4*16位的,支援 LPDDR4,整合了 Gen 11 內顯,有64個EU單元,Gen 11.5 的顯示控制器還有新的 IPU,並且支援 DP 1.4。

位於底部的基底層作為 SoC 的快取與 I/O 模組,應該整合了 PCI-E 控制器並擁有 PCH 晶片的部分功能,為 SoC 提供豐富的 I/O 功能,由於 SoC 直接整合了記憶體模塊,所以可以讓移動設備的主板變得更為小巧,而 Lakefield SoC 本身也只有12*12mm那麼大,TDP 不會高於7W,它的出現可以讓未來的移動設備變得更輕薄,並且有更強的續航能力。

但是目前還不知道這個 Lakefield SoC 是否需要搭配 PCH 所使用,因為從上圖來看 SoC 下面那個大晶片看起來像是 PCH,不過目前無法確定。

來源:https://www.expreview.com/67009.html