Intel 最近在美國加州聖克拉拉舉行的數據中心創新峰會上承認了10nm製程要推到2019年,另外在銜接10nm之前的空窗還會有14nm++的 Cooper Lake。

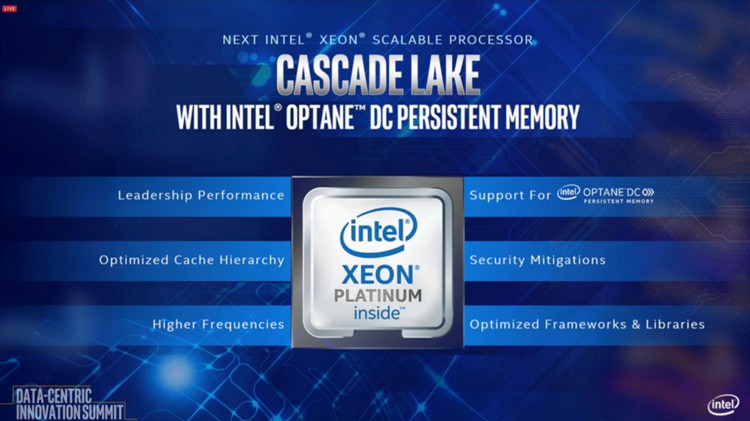

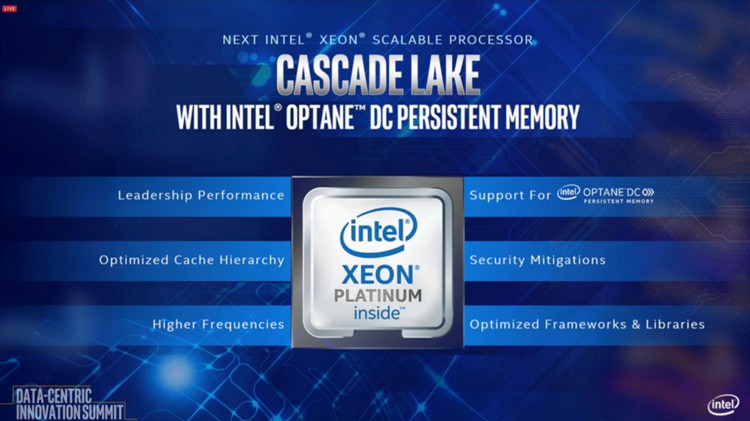

Tomshardware表示今年 Intel 會推出基於 Cascade Lake 架構的 Xeon 處理器並利用其更新 HEDT 平台的產品,與現在的 Skylake 架構 Xeon 相比生產製程算是有所改良,並且集成了一個新的記憶體控制器,主要是為了支援新的 Optane DIMM,並且從晶片架構上修復了幽靈和熔斷兩個漏洞,這次的漏洞修復可能會刺激資料中心的產品更新換代。

Cascade Lake 會對處理器的快取進行優化,其實 Skylake-X / SP 處理器上 Intel 已經對快取進行了一次修改,增大了獨享的 L2 快取減少了共享的 L3,不過效果不太明顯,不知道這次又會有甚麼差異性,此外 Cascade Lake 還會加入對 DLBoost 的支援,這是針對機器學習應用的 AVX -512 指令集的優化。

明年 Intel 會推出 Cooper Lake,採用14nm++製程,這算是 Intel 在10nm投產前的一個權宜之計,Cooper Lake-SP 處理器將採用 Google 新的浮點格式 Bfloat 16,並且會與2020年推出的 10nm Ice Lake-SP 採用同樣的平台,也就是說 Cooper Lake-SP 處理器將使用 LGA 4198 接口。

來源:

https://www.tomshardware.com/news/intel-roadmap-cooper_lake-ice_lake,37574.html

http://www.expreview.com/63329.html

Tomshardware表示今年 Intel 會推出基於 Cascade Lake 架構的 Xeon 處理器並利用其更新 HEDT 平台的產品,與現在的 Skylake 架構 Xeon 相比生產製程算是有所改良,並且集成了一個新的記憶體控制器,主要是為了支援新的 Optane DIMM,並且從晶片架構上修復了幽靈和熔斷兩個漏洞,這次的漏洞修復可能會刺激資料中心的產品更新換代。

Cascade Lake 會對處理器的快取進行優化,其實 Skylake-X / SP 處理器上 Intel 已經對快取進行了一次修改,增大了獨享的 L2 快取減少了共享的 L3,不過效果不太明顯,不知道這次又會有甚麼差異性,此外 Cascade Lake 還會加入對 DLBoost 的支援,這是針對機器學習應用的 AVX -512 指令集的優化。

明年 Intel 會推出 Cooper Lake,採用14nm++製程,這算是 Intel 在10nm投產前的一個權宜之計,Cooper Lake-SP 處理器將採用 Google 新的浮點格式 Bfloat 16,並且會與2020年推出的 10nm Ice Lake-SP 採用同樣的平台,也就是說 Cooper Lake-SP 處理器將使用 LGA 4198 接口。

來源:

https://www.tomshardware.com/news/intel-roadmap-cooper_lake-ice_lake,37574.html

http://www.expreview.com/63329.html