AMD 的下一代 Zen 5 架構 Ryzen 行動處理器代號為 Strix Point 以及一個大型的 APU — Strix Halo,當中 Strix Point 已經確定會在今年年內推出,而 Strix Halo 還不確定,可能是今年,也有可能在明年的 CES 上推出,它擁有多達16個 Zen 5 CPU 核心和40個 RDNA3+ CU 的 GPU,主要是做為遊戲與 AI 應用筆電的移動版處理器。

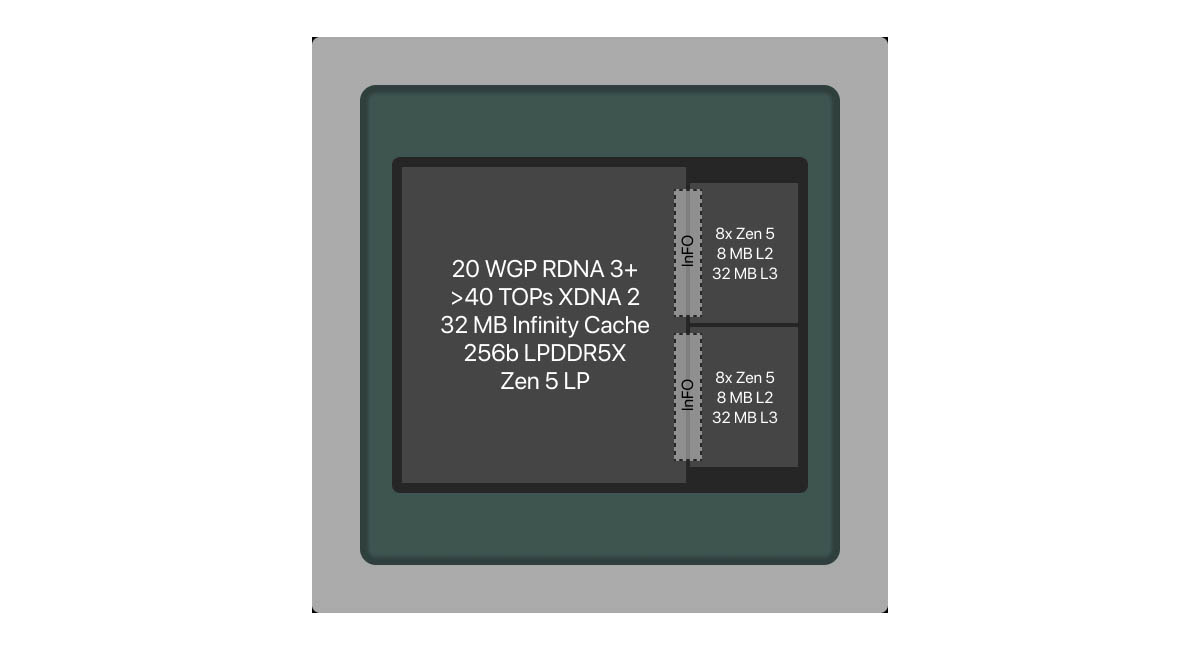

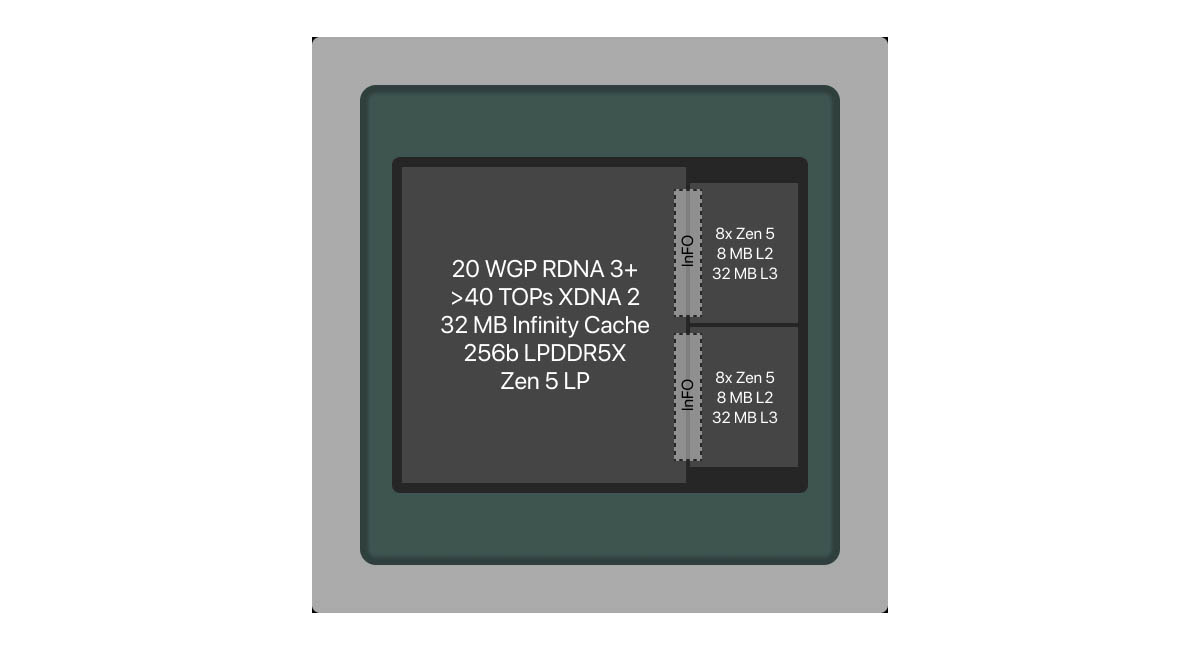

最近 Strix Halo 的核心渲染圖曝光,這個 APU 採用 MCM 設計,共有三顆晶片,有兩個 CCD 和一個 GCD,Zen 5 架構每核心擁有 1MB 的 L2 快取,每個CCD擁有8個核心,32MB L3 快取,所以一共有 6MB L2 快取和 64MB L3 快取,兩個 CCD 使用 IF 匯流排與 GCD 連接。

IOD 被 GCD 取代,實際上它也算是個整合了較大規模內顯的 IOD,它的晶片面積非常大,比兩個 CCD 大得多,它除了整合了40組 CU 的 RDNA3+ 架構 GPU 外,還有算力超過 40 TOPS 的 XDNA 2 架構 NPU,32MB MALL Cache ,還有256位元的 LPDDR5x 記憶體控制器,而且可能還配備了 Zen 5 LP 核心。

目前的 RX 7600 XT 也只有32組 CU,Strix Halo 上這個40組 CU 的內顯規模可以說相當巨大,但它並沒有像遊戲主機 SoC 那樣直接使用 GDDR6 作為記憶體,而是使用 LPDDR5x,最高頻率 8000MHz ,但對於現在的 GPU 來說頻寬還是太低了,所以加入了 32MB MALL Cache 來緩解記憶體頻寬不足的問題。

從先前曝光的資訊來看,Strix Halo 的標準 TPD 應該是 70W,廠商可以根據設備的散熱設計進行改動,最高可以把 CPU TPD 調到 130W 以上,採用 FP11 平台,支援 DP2.1 和 UHBR20 視訊輸出。

來源

最近 Strix Halo 的核心渲染圖曝光,這個 APU 採用 MCM 設計,共有三顆晶片,有兩個 CCD 和一個 GCD,Zen 5 架構每核心擁有 1MB 的 L2 快取,每個CCD擁有8個核心,32MB L3 快取,所以一共有 6MB L2 快取和 64MB L3 快取,兩個 CCD 使用 IF 匯流排與 GCD 連接。

IOD 被 GCD 取代,實際上它也算是個整合了較大規模內顯的 IOD,它的晶片面積非常大,比兩個 CCD 大得多,它除了整合了40組 CU 的 RDNA3+ 架構 GPU 外,還有算力超過 40 TOPS 的 XDNA 2 架構 NPU,32MB MALL Cache ,還有256位元的 LPDDR5x 記憶體控制器,而且可能還配備了 Zen 5 LP 核心。

目前的 RX 7600 XT 也只有32組 CU,Strix Halo 上這個40組 CU 的內顯規模可以說相當巨大,但它並沒有像遊戲主機 SoC 那樣直接使用 GDDR6 作為記憶體,而是使用 LPDDR5x,最高頻率 8000MHz ,但對於現在的 GPU 來說頻寬還是太低了,所以加入了 32MB MALL Cache 來緩解記憶體頻寬不足的問題。

從先前曝光的資訊來看,Strix Halo 的標準 TPD 應該是 70W,廠商可以根據設備的散熱設計進行改動,最高可以把 CPU TPD 調到 130W 以上,採用 FP11 平台,支援 DP2.1 和 UHBR20 視訊輸出。

來源