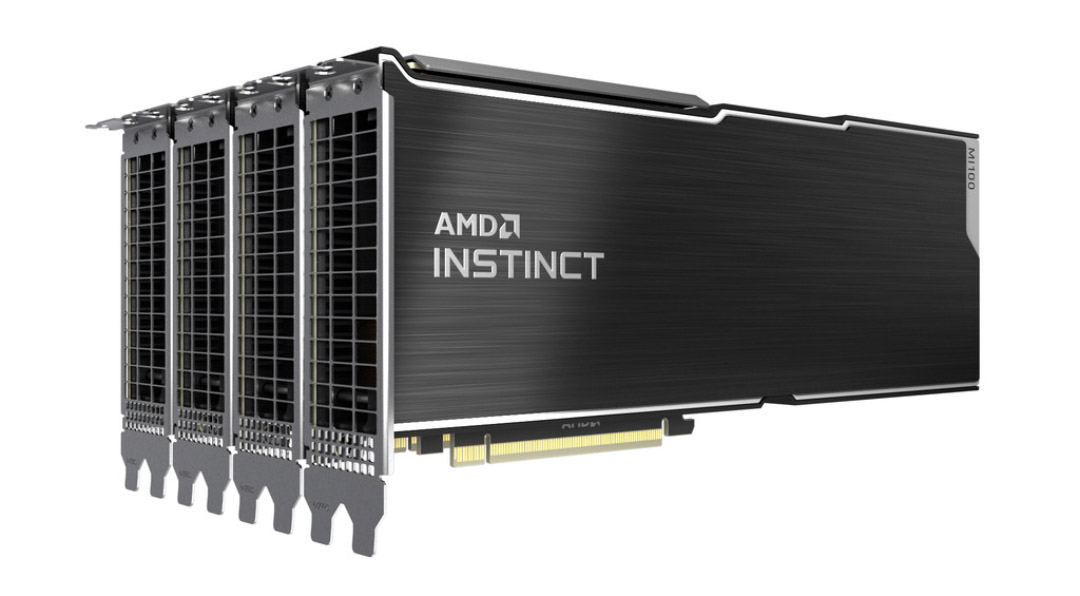

AMD Instinct M1100加速器徹底改變了高性能計算 (HPC) 和 Al具有業界領先的計算性能

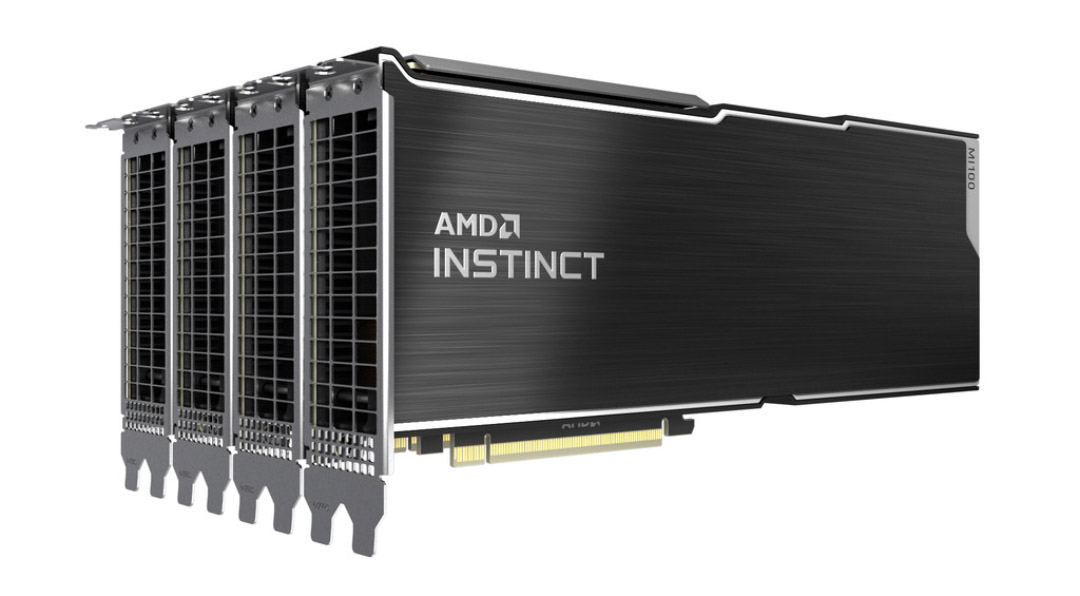

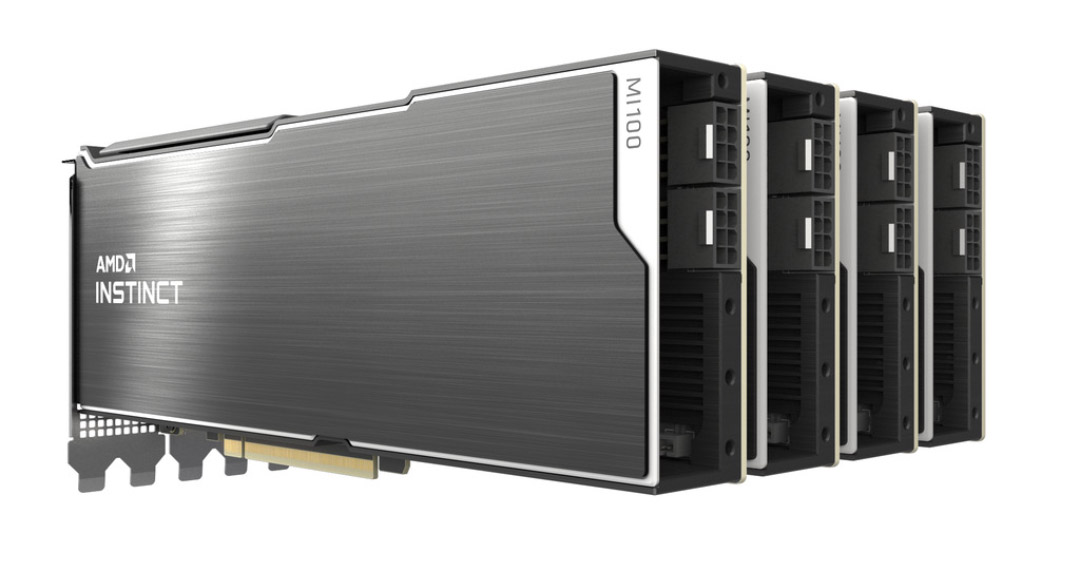

AMD Instinct M1100加速器

AMD Instinct MI100加速器是第一個 GPU加速器,其新型 AMD CDNA架構專為超大規模時代設計,基於新的 AMD CDNA架構構建,與第二代 AMD EPYC處理器配對時,用於 HPC和 Al的加速系統

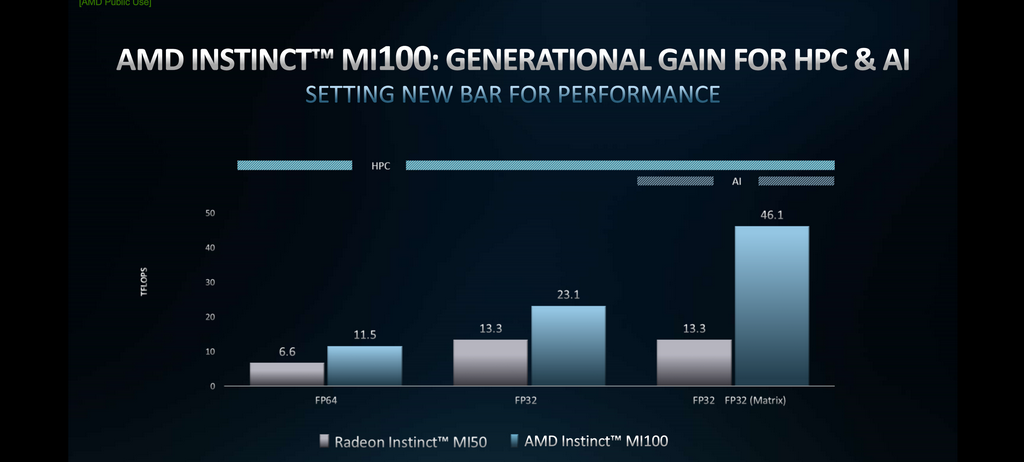

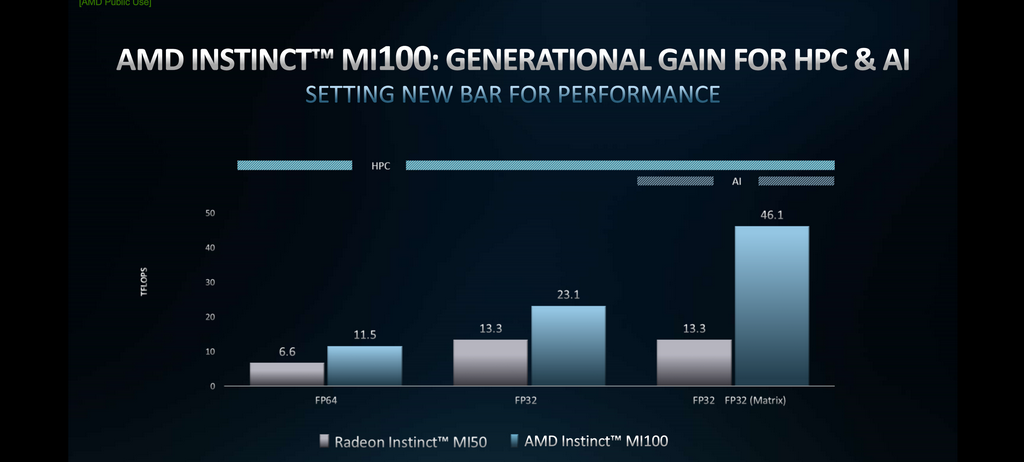

AMD Instinct MI100加速器提供高達 11.5 T FLOPS的峰值 FP64性能為 HPC和高達 46.1TFLOPS峰值 FP32矩陣,Al和機器學習工作負載的性能,使用新的 AMD矩陣核心技術

AMD Instinct MI100加速器也為 Al培訓提供了近 7倍的 FP16理論峰值浮點性能提升

AMD針對在科學計算,結合 AMD ROCm開放軟體平臺,旨在為科學家和研究人員在 HPC中的工作提供卓越的基礎,並朝百萬兆級運算時代邁進

AMD Instinct MI100加速器性能諸元

AMD Instinct MI100加速器是新一代領頭之 HPC產品,擁有 7nm Vega架構的增強版本,亦為當前最新推出的加速器,在 GPU方面亦是 AMD CDNA組合中最重要的 HPC產品,支援生態系統無國界

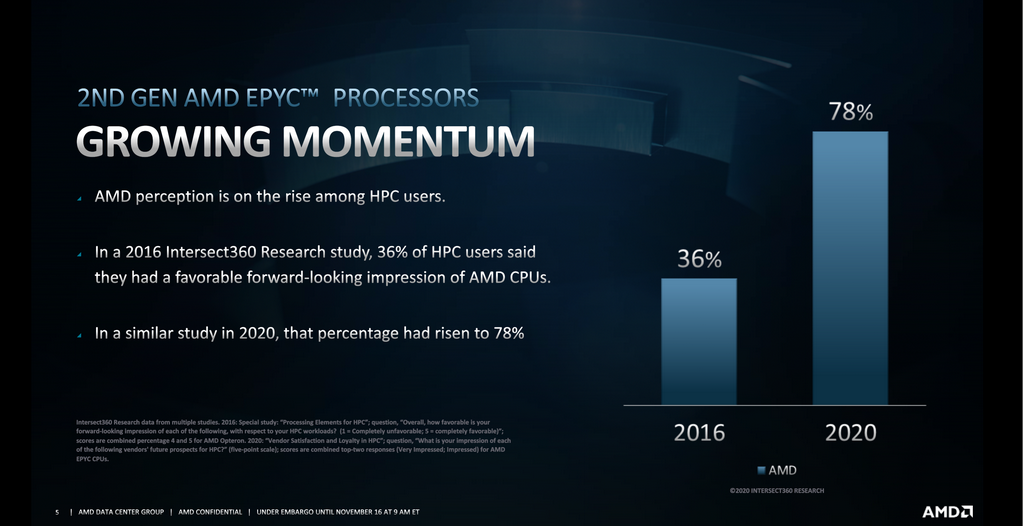

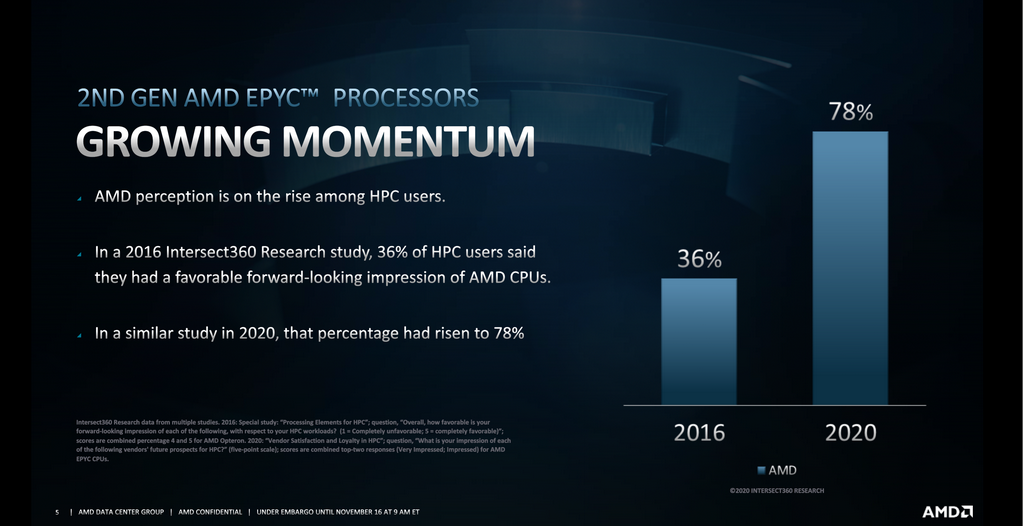

第 2代 AMD EYPC之動量成長

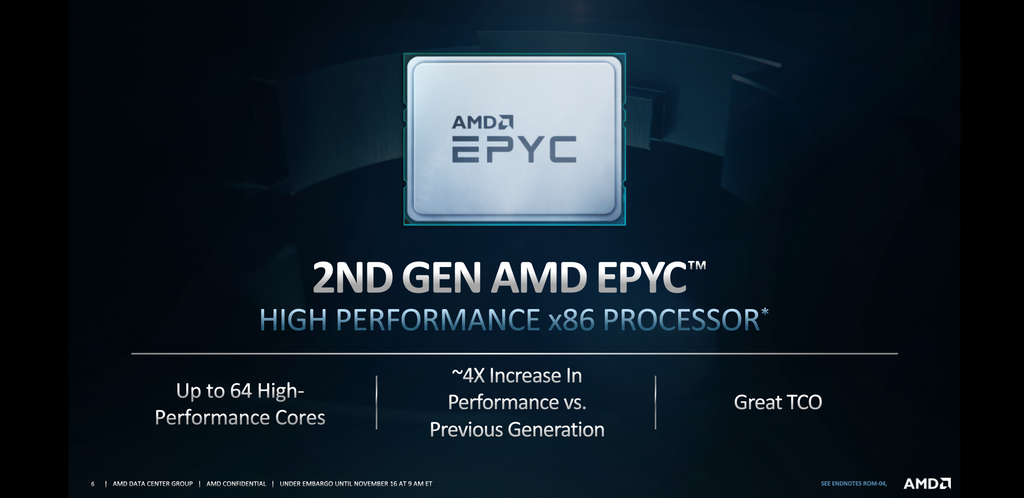

第 2代 AMD EYPC擁有 64 Cores,4倍效能增長

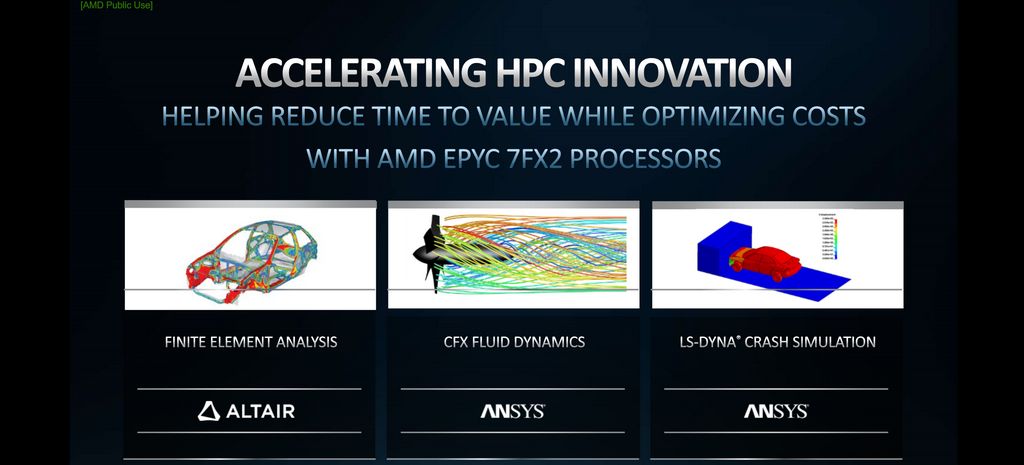

HPC的負載是多元化的,並定位在多線程負載以滿足各在領域用戶的需求

CFX高頻處理器具有極高的運算性能跟上一代相比有提升 54%

3家廠商使用 AMD EPYC作生產及研究獲得很高的效益

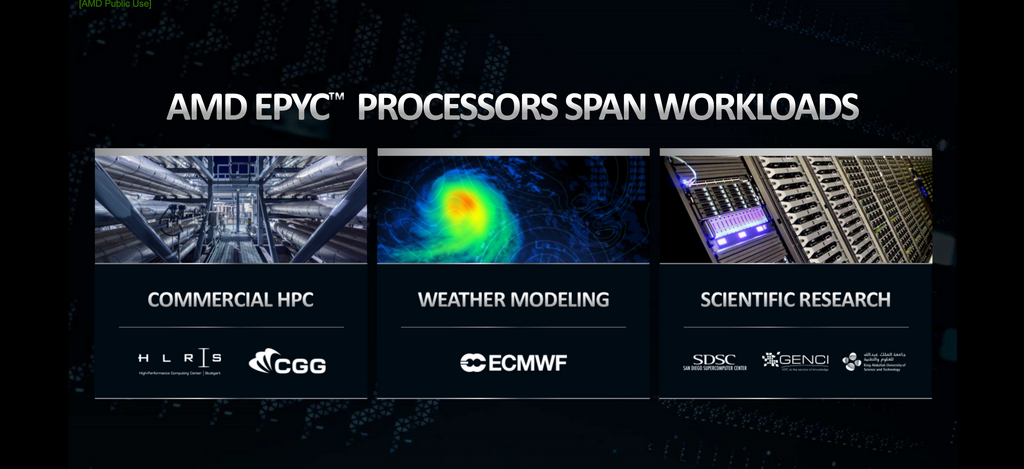

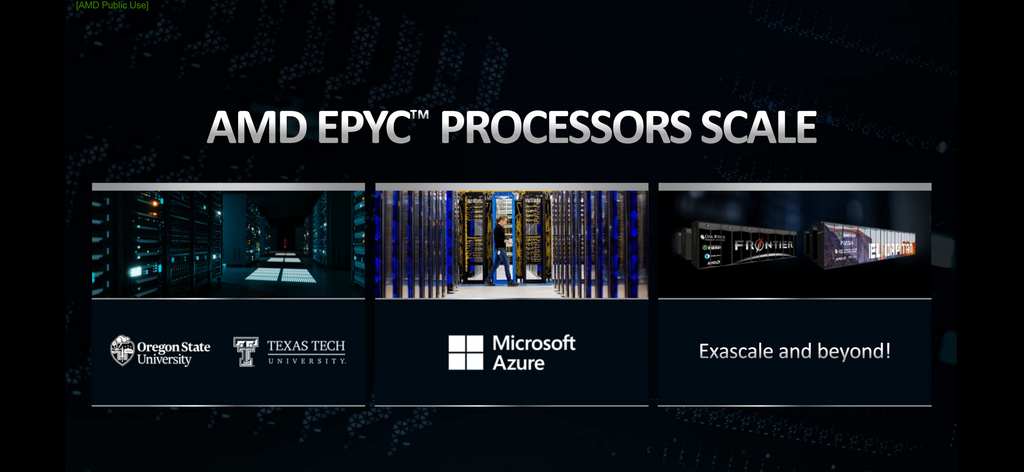

在不同的工作負載上 AMD EPYC都能輕易的勝任

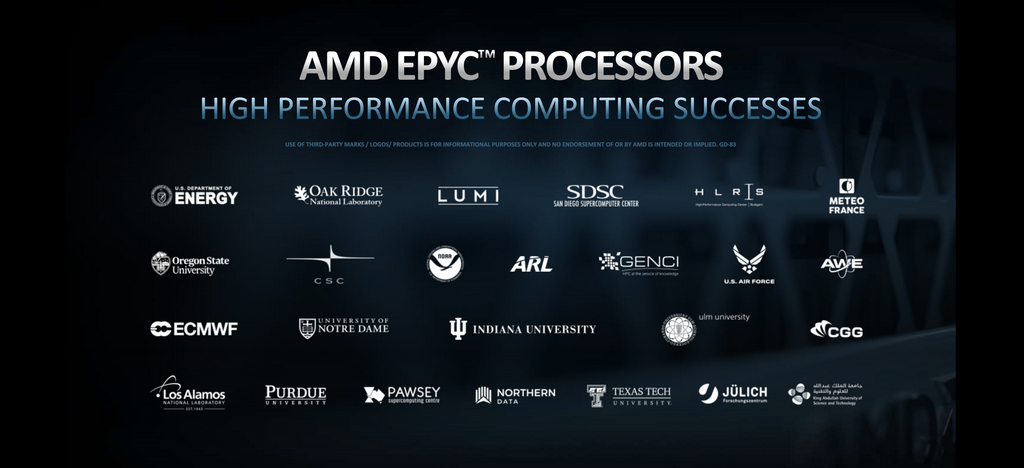

許多客戶成功案例,尤以 CGG、LUMI等最為出色

AMD正按計畫做第三代 EPYC OEM服務器之發布

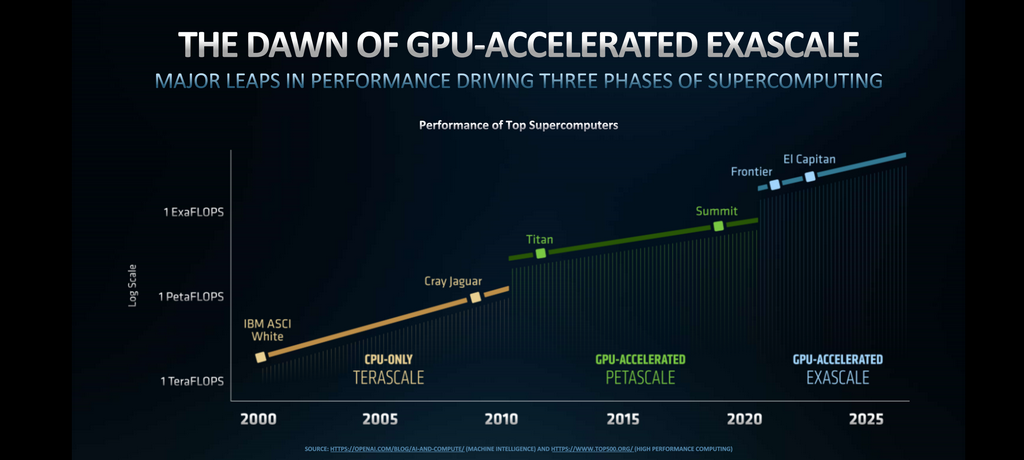

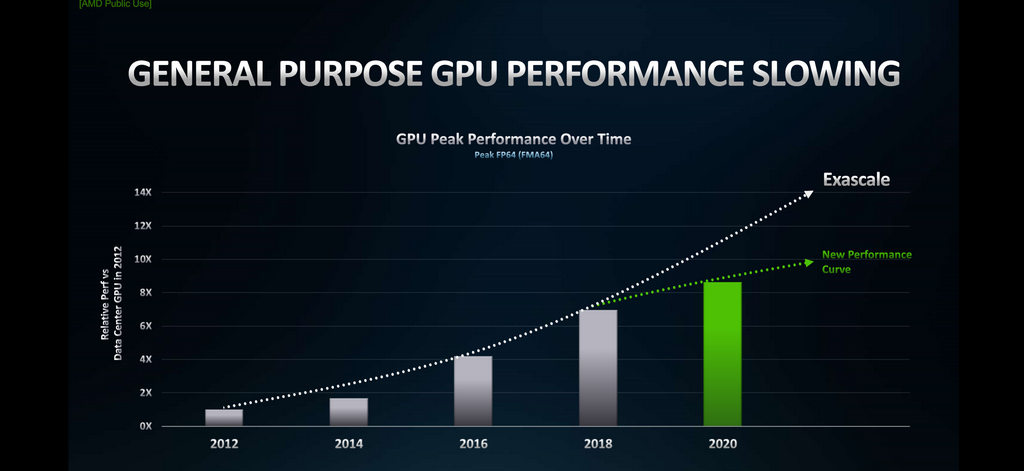

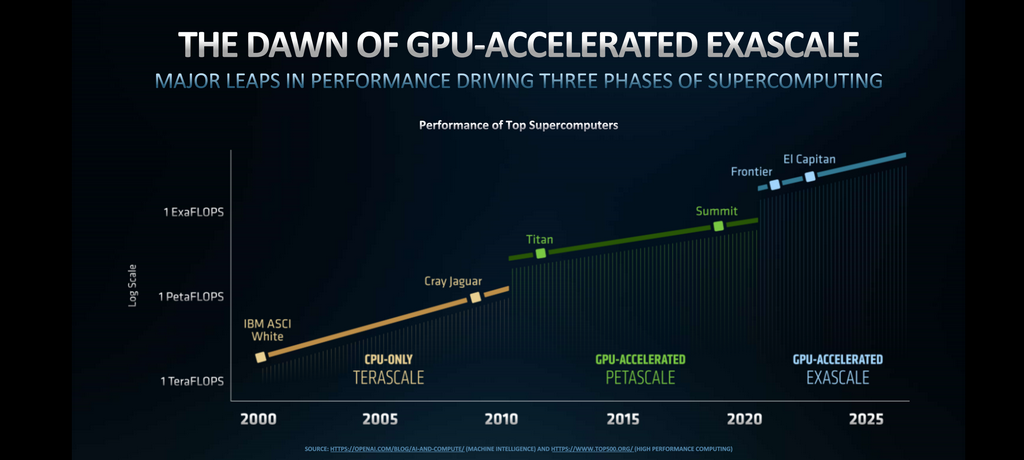

20年來的 3個階段進程,將在 2025年達成 Exascale百萬兆級運算,Exascale百萬兆級運算指的是每秒可執行100萬兆次 (1 exaflops) 的運算,Exascale百萬兆級系統的效能可達現在最強大電腦的 50倍

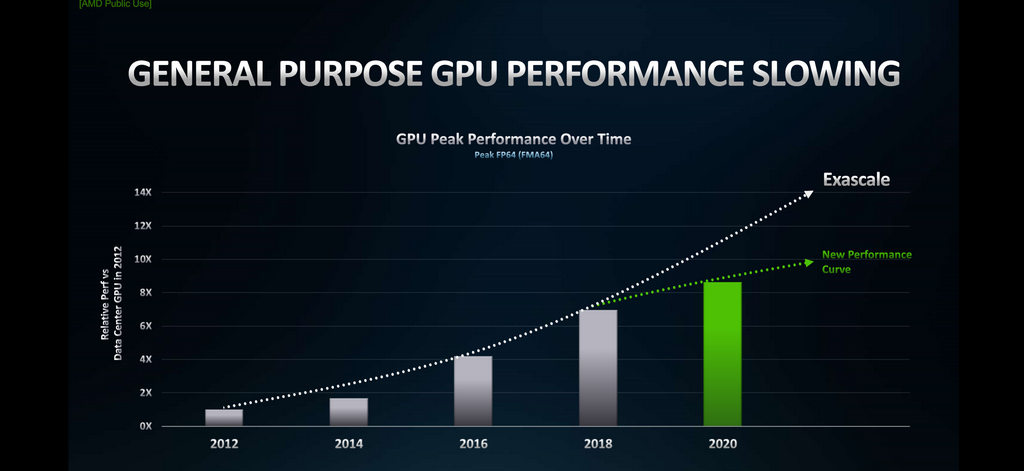

AMD並改善了 GPU Peak Performance曲線成長趨緩的問題

AMD Instinct MI100加速器是針對高性能最快產品能實現超過 10TF資料處理,通過關鍵的優化和增強的可擴充性為數據中心提供動力

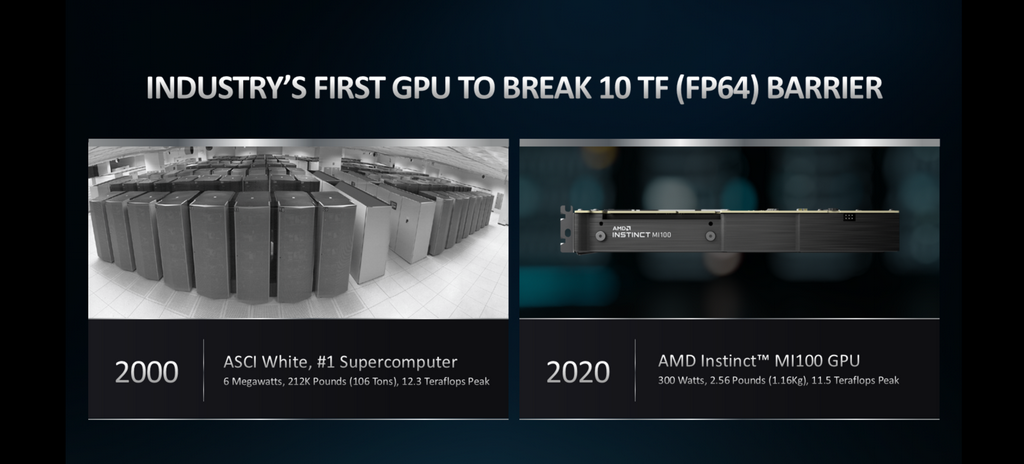

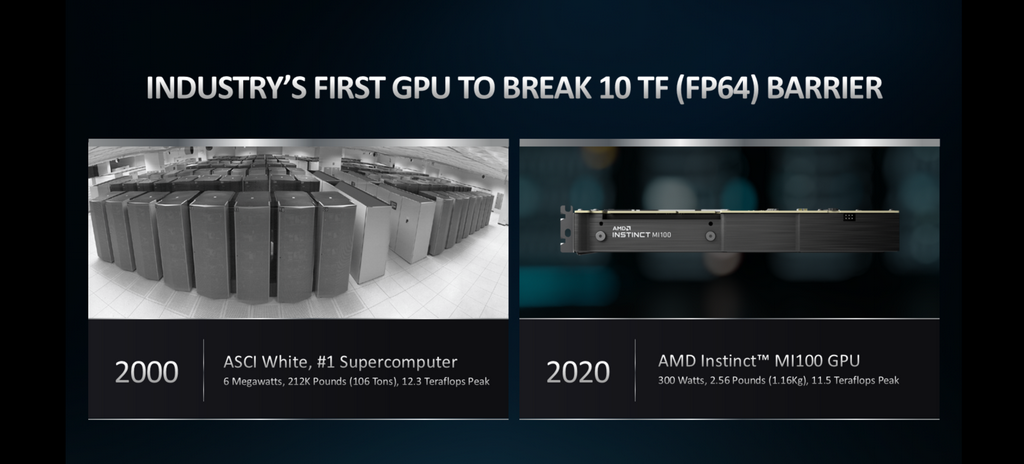

20年前的 ASCI與 2020年的 Instinct MI100加速器量體比較

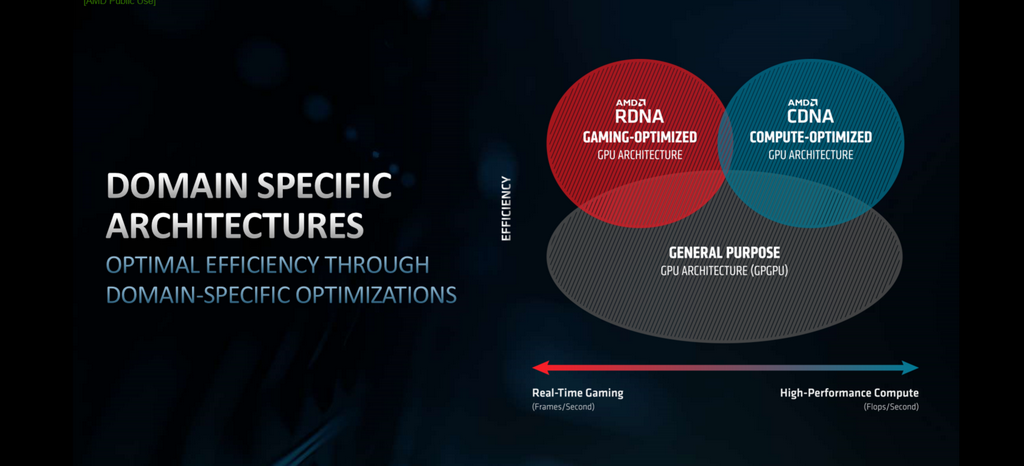

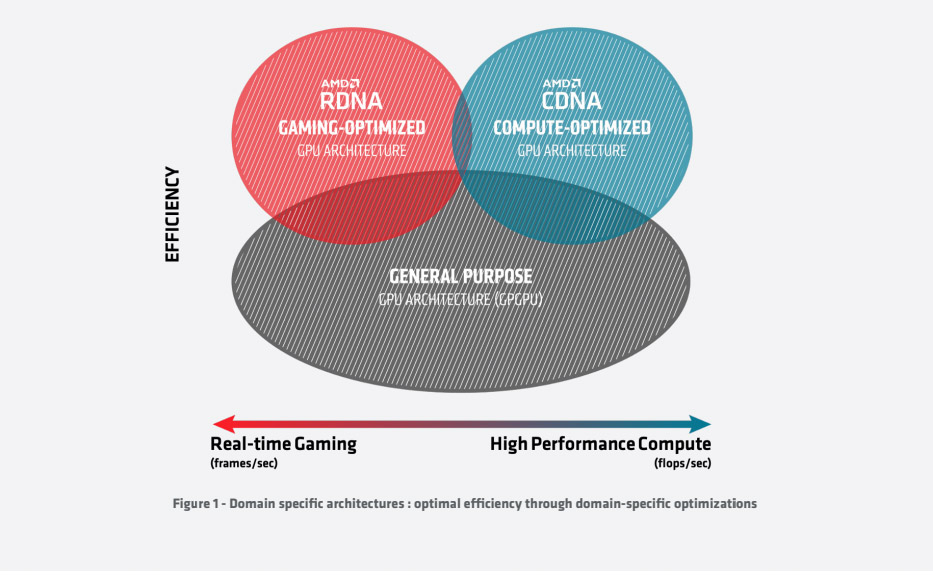

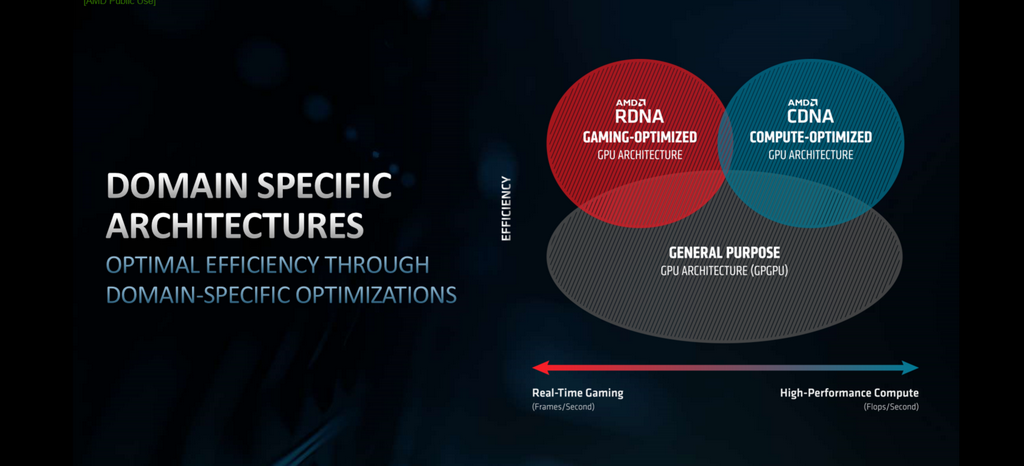

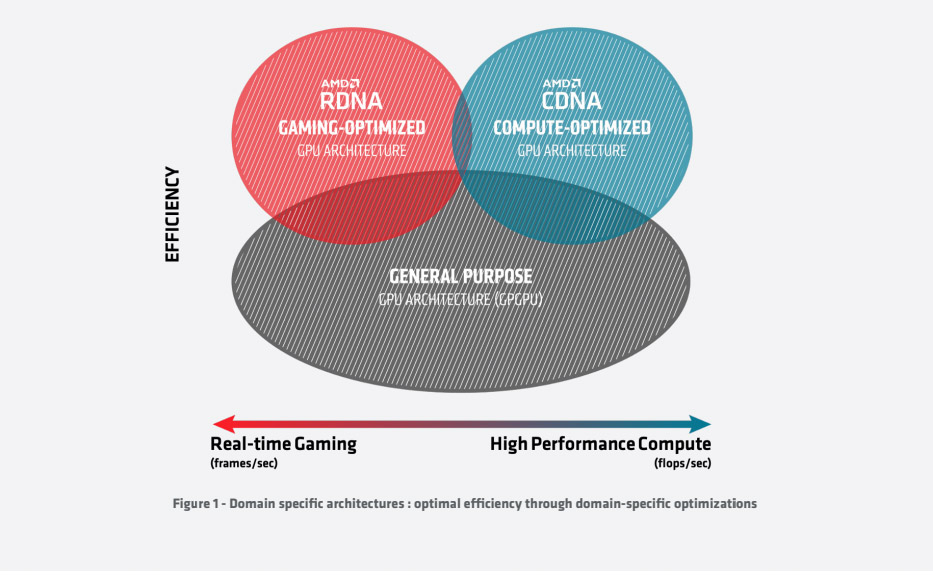

GPU各個架構驅動不同用途負載比如高效能運算或在即時遊戲中各司其職

在過去的三十年中,圖形處理器已經從專門的固定功能架構發展成為完全可程式設計的架構加速器。雖然早期的設計側重於有限的計算,如照明轉換,今天的 CPU是通用的並交付了計算豐富的軟體,如應用程式和福特蘭 C++性能提升,行業同時演變為利用 CPU的關鍵領域,如機器學習和科學計算 – 這將推動創新幾十年在技術層面上,這轉化為硬體和軟體的兩大趨勢,首先,CPU已經從固定函數管道,以靈活的計算引擎,如 GCN架構,提供標量和向量處理。同時軟體生態系統已迅速擴展,通過提供關鍵工具,包括從數學庫和編譯器到調試器,到群集管理和部署,一切

AMD為從 PC遊戲玩家到數據中心平臺等廣泛的用例構建高性能計算解決方案,而傳統的 CPU被構建為一般用途,旨在推動面向圖形和面向計算的工作負載,AMD最近推出了一種不同的方法來提高效率,現在有兩種架構:AMD RDNA針對遊戲進行了優化,以最大化每秒幀數,AMD CDNA針對計算進行了優化,以突破每秒 flops的限制

AMD CDNA架構

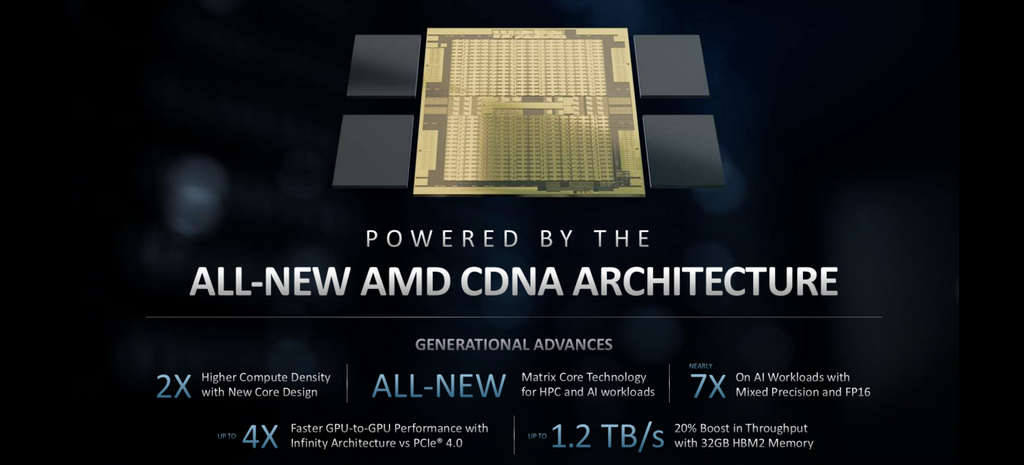

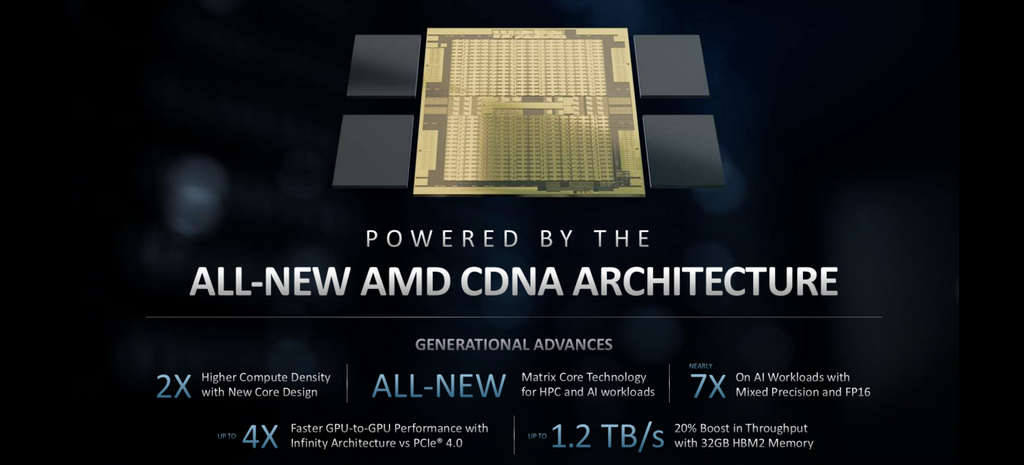

CDNA的主要重點是增強數據中心的效能、效率、功能和可擴充性,藉助 CDNA,AMD將創建專門針對高性能計算,機器學習和 HPC優化的GPU,首款採用 CDNA架構之產品 2X運算單元 AI FP16 PCIe 4.0 4X頻寬,記憶體頻寬達 1.2TB/s

AMD Instinct MI100加速器在 for HPC & AI單雙精度運算性能比較上,AMD Instinct MI100加速器可實現百億億次級以上的雙精度處理能力

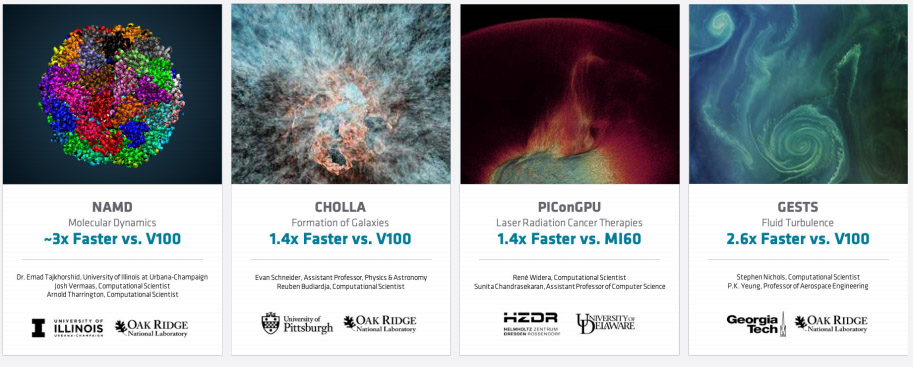

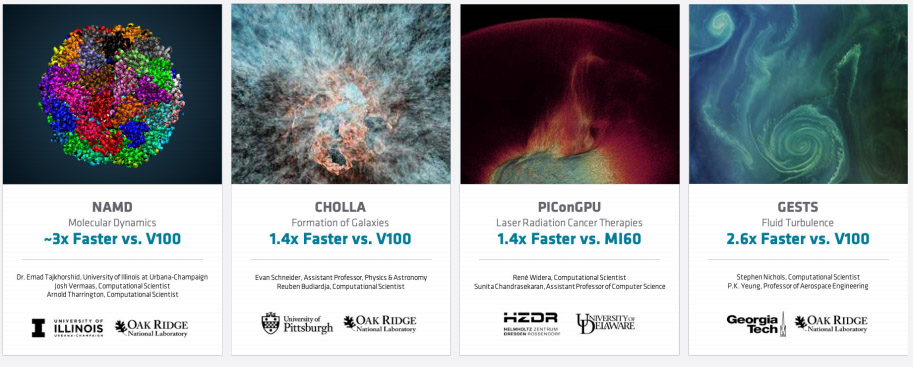

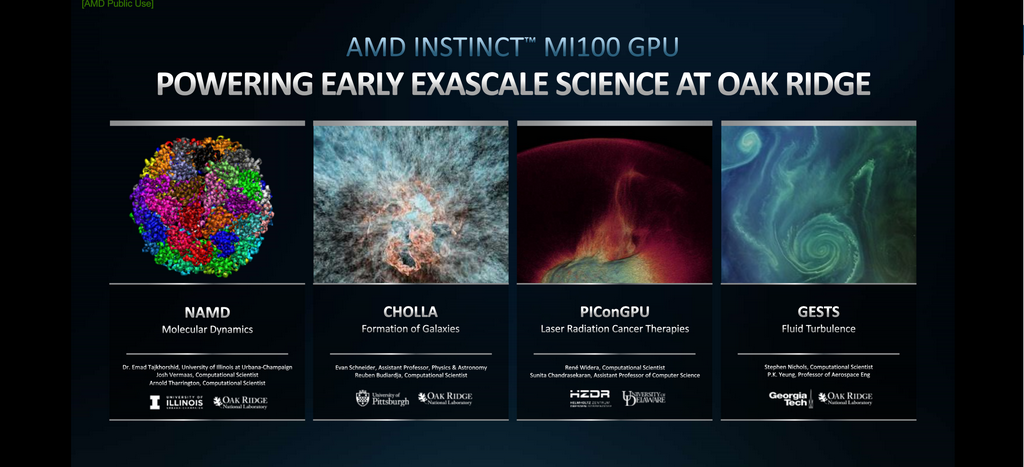

AMD Instinct MI100加速器在 Open Souce之各工作負載上的表現

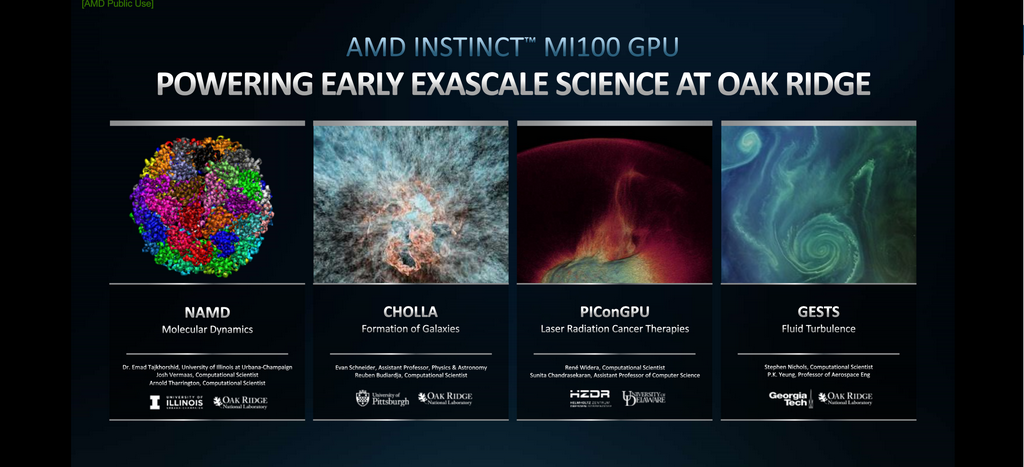

生物研究團隊研究蛋白質工程以產生新的產業,設計新的藥物和醫學療法來改善人類的生活,氣候科學家並藉此模擬世界海洋與大氣的行為,建立氣候急劇變化的模型,幫助我們瞭解我們需要做些什麼來使地球一直作為一個適宜生存和舒適的地方,科學家正在以盡可能小的規模研究材料的性質,從發電與輸電到生產速度更快、體積更小、功能更多的計算機和儲存裝置

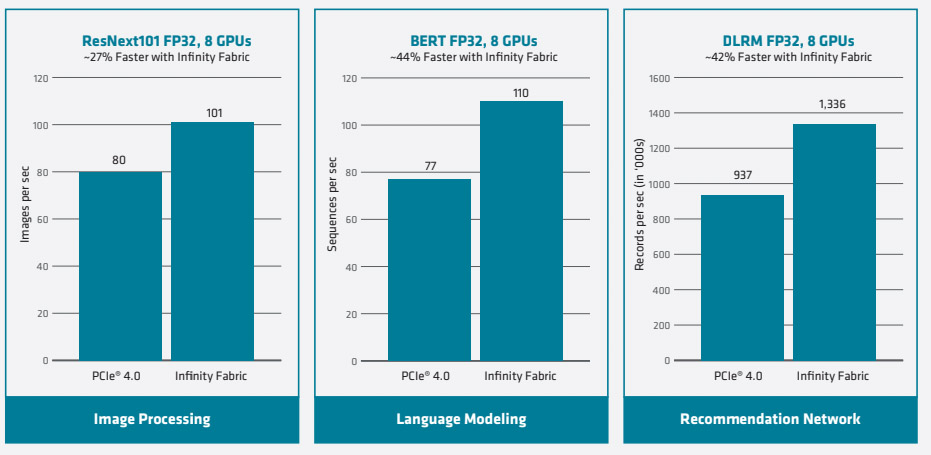

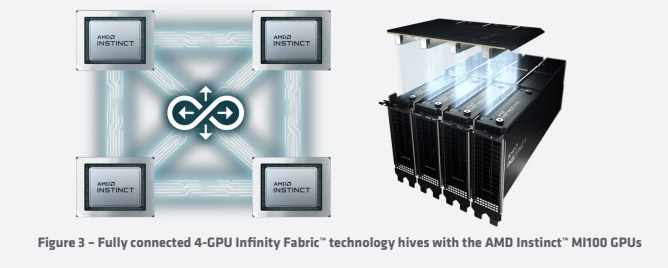

使用 AMD Infinity結構改進 HPC和 Al性能

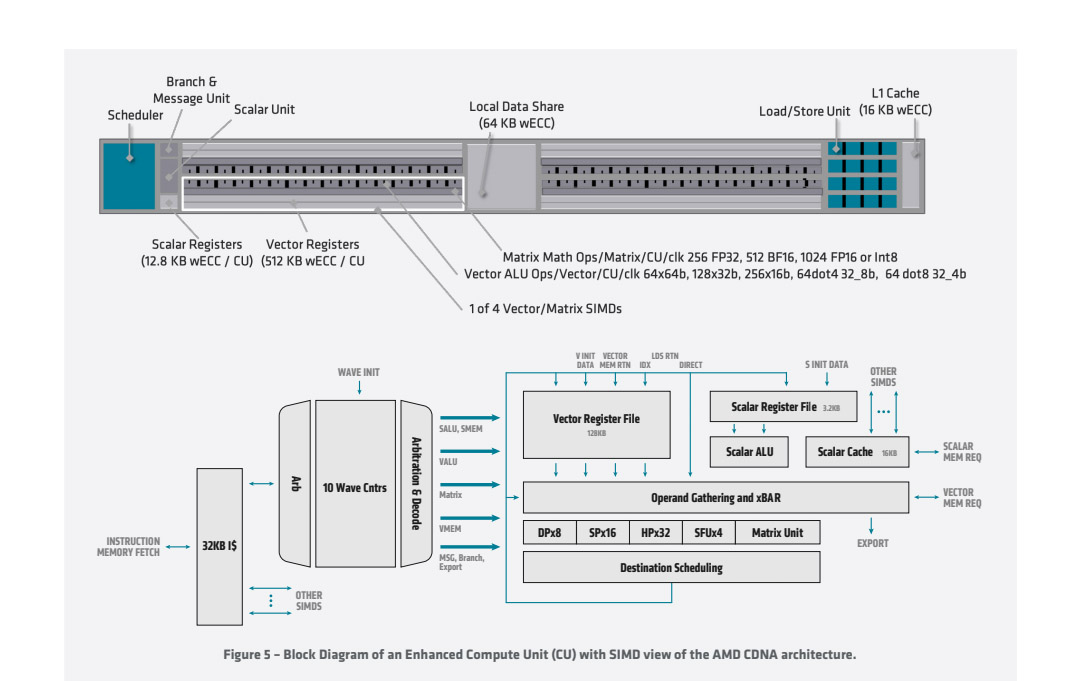

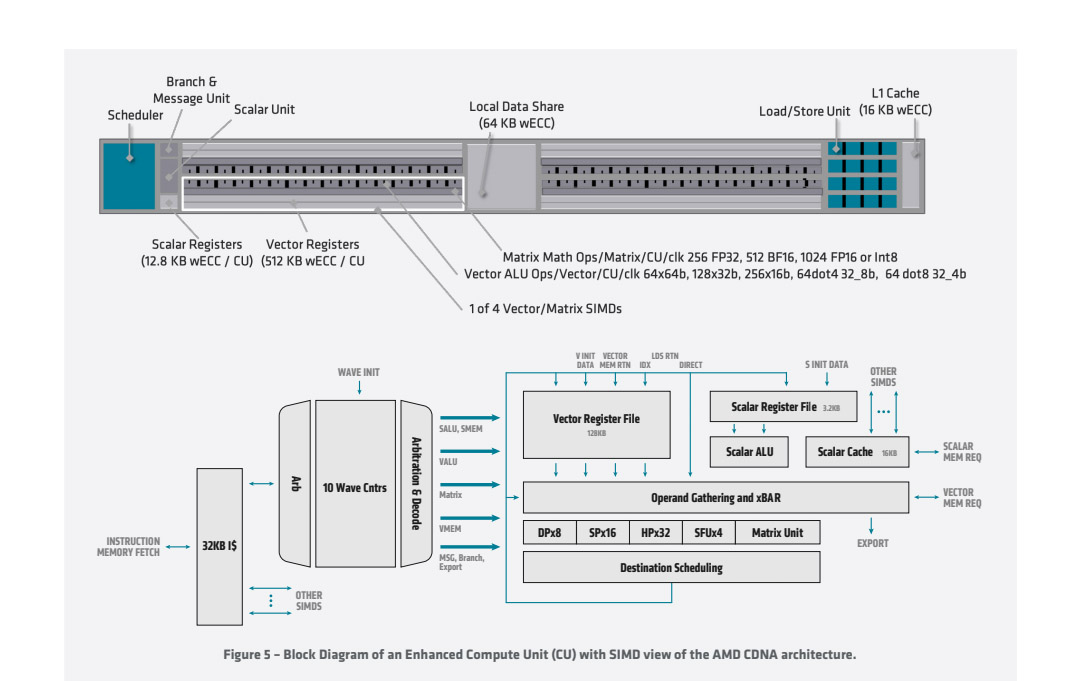

AMD CDNA架構計算單元

命令處理器和調度邏輯將更高級別的 API命令轉換為計算任務,這些計算任務反過來以計算陣列方式實現,並由非同步計算引擎 (ACE) 管理,四個 (ACE) 中每個都維護獨立的命令流,可以向計算單元調度

AMD CDNA架構的令人印象深刻的 120個 Cus,被組織成四個 CUs陣列,CUs派生自較早的 GCN體系結構和執行包含 64個工作項目,但是,使用新的矩陣核心引擎來增強針對執行對矩陣數據類型進行操作的計算內核進行了優化,提高了計算輸送量和能效

經典的 GCN計算內核包含針對標量和向量指令優化的各種管道,特別是每個 CU包含標量寄存器檔、標量執行單元和標量數據緩存,用於處理跨波前共用的指令,例如常見的控制邏輯或位址計算。同樣 4個向量執行單元也包含一個大型向量寄存器檔,針對 FP32和向量數據緩存進行了優化,通常,向量管道為 16-wide,每個 64-wide的 wavefront在四個週期

AMD CDNA架構基於 GCN的標量和向量基礎,並增加了矩陣作為一流的陣容,而同時為機器學習的新數位格式添加支援,並保留任何軟體的向後相容性

為 GCN架構編寫這些矩陣核心引擎增加了一個新的指令系列,矩陣融合乘法-添加或 MFMA系列執行混合精度術,並使用五種不同類型的輸入在 KxN矩陣上操作

數據: 4bit整數(INT4)、8bit整數 (INT8)、16bit半精度 FP (FP16)、16bit brain FP (bf16) 和 32bit單精度 (FP32)

所有 MFMA指令都會生成 32bit整數 (INT32) 或 FP32輸出,從而降低最終輸出期間溢出的可能性矩陣乘法的累積階段

不同的數位格式都有不同的推薦應用。業界普遍認為,INT8數位是主要用於具有量化權重或數據的 ML推理,並且具有最佳輸送量和最低記憶體使用量。相比之下,大多數 ML訓練和某些 HPC應用程式預設使用 IEEE FP32資料,其中 8bit分配給指數範圍和 23bit用於捕獲精度的尾數,FP16是另一個 IEEE標準,專為圖形工作負載而設計,使用 5bit指數和 10bit,雖然 FP16比 FP32 效率更高,但縮小的範圍並不總是開箱即用,對於 ML訓練有時需要調整演演演算法以避免溢出和收斂問題

120個增強型計算單元 (CUs) 建立在 GCN架構的基礎上,並組織成四個計算引擎,以及負責 AMD Instinct MI100加速器中的所有計算,雖然受到上一代 CCN架構的啟發,但每個 CU使用矩陣核心引擎進行重新設計並增強,可顯著提高多種不同的數位的計算輸送量格式。在所有 CU中,Instinct MI100加速器可以實現理論雙精度浮點輸送量高達 11.5TFLOP/s – 第一個打破 10TFLOP/s障礙的處理器。不像面向圖形的 AMD RDNA系列,AMD CDNA系列移除所有旨在加速圖形任務的固定功能硬體,如閘格化、細分、圖形快取、混合,甚至顯示引擎,但是,AMD CDNA系列保留了 HEVC、H.264和 VP9解碼的專用邏輯,即有時用於對多媒體數據進行操作的計算工作負載,例如用於物件檢測的機器學習?刪除固定功能圖形硬體可釋放面積和動力,以投資額外的計算單元,從而提高性能和效率

L2 Cache和記憶體

AMD Instinct MI100加速器記憶體層次結構的最低級別位於 CUs,但大多數科學或機器內學習數據集以千兆位元組或 TB為單位進行測量,並快速溢出到記憶體中,記憶體層次結構負責持有工作數據,並有效地將數據傳遞到計算中消耗數據的計算陣列

L2 Cache在整個晶元中共用,並物理分區為多個切片。對於 Instinct MI100加速器,Cache為 16way設置-關聯,包括 32個切片(是 MI50的兩倍),總容量為 8MB,每個切片可以維持 128B超過 6TB/s的 CPU聚合頻寬

AMD CDNA架構針對要求最苛刻的工作負載而設計,記憶體控制器和介面專為最大頻寬、能效和極高的可靠性,記憶體控制器驅動 4或 8個的共同封裝 HBM2堆疊為 2.4CT/s,理論輸送量為 1.23TB/s ,比上一代 AMD加速器快 20%,同時保持 CPU功率預算常數。HBM2記憶體的 32GB受強大的 ECC保護,使關鍵任務應用程式能夠大規模運作

溝通和擴展

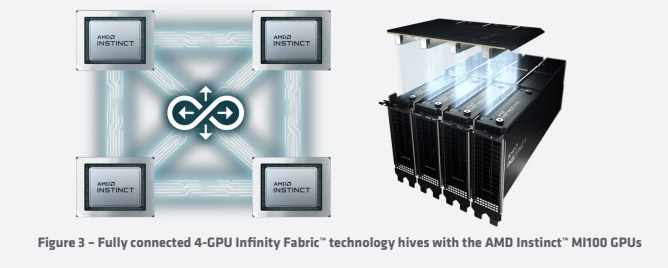

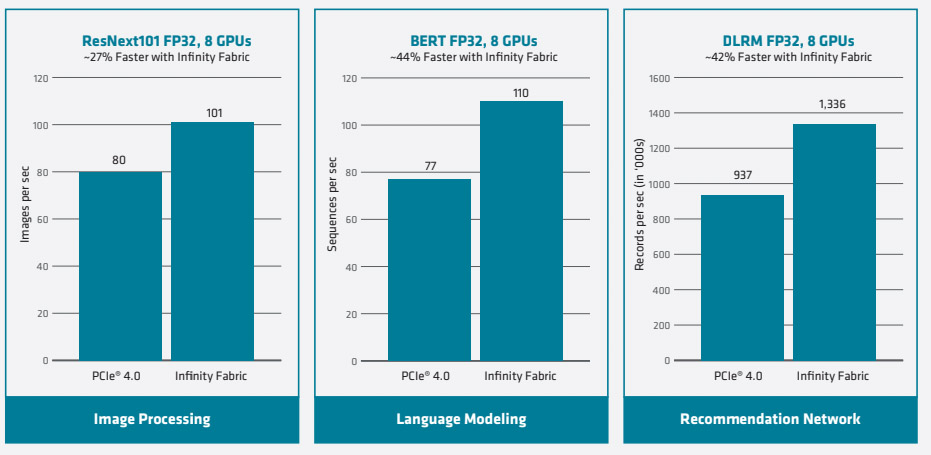

系統體系結構的最後一部分是通信,以跨多個 CPU進行擴展。雖然運行小型工作負載的系統可能使用單個 AMD Instinct MI100加速器, 更大和更苛刻的問題, 如訓練神經網路需要更強大系統,例如,用於語言建模的 BERT神經網路可擴展到最多數千個處理器最近的 MLPerf Benchmark AMD CDNA架構使用基於標準的高速 AMD無限交換矩陣技術連接到其他 CPU Infinity fabric鏈路以 23CT/s 運行,與上一代鏈路寬 16bit,但 MI100帶來了第三個鏈路,用於在四 CPU配置提供更大的雙節頻寬,並支援高度可擴展的系統,與 PCIe不同,AMD Infinity Fabric連結支援一致的 CPU記憶體,使多個 CPU能夠共用一個位址空間,並在單個問題上緊密配合

利用新的矩陣引擎增強節能

與 GCN中的傳統向量管道相比,矩陣執行單元具有若干優勢

第一:執行單元減少寄存器檔讀取的數量,因為在矩陣乘法中,會重新使用許多輸入值

第二:較窄的數據類型為不需要完全 FP32精度的工作負載(例如機器學習)創造了巨大的機會,一般來說,能量乘積操作消耗的是輸入數據類型的平方,因此從 FP32到 FP16或 bf16的轉換可以節省巨大的能量

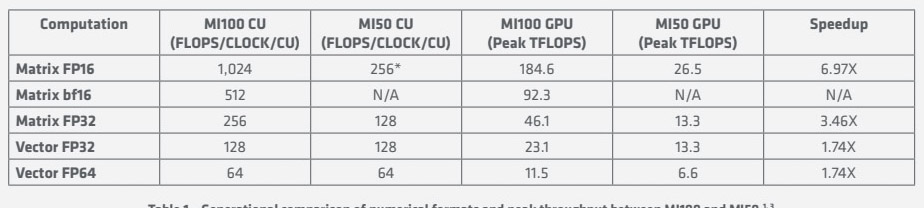

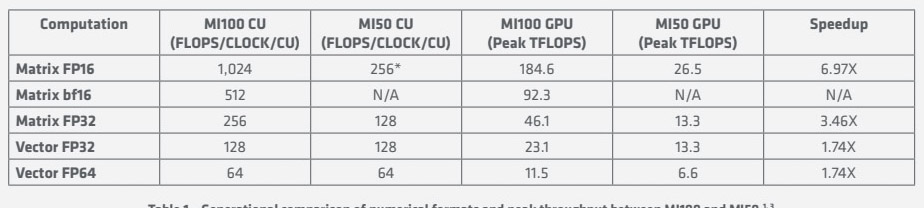

MI100和 MI50之間的數位格式和峰值輸送量的代際比較

對向量執行單元執行矩陣操作,上表描述了使用傳統向量指令和新的矩陣乘法指令在 MI50與 MI100的比較,新指令和執行資源的最終結果是對於矩陣計算,MI100保持與上一代類似的功率配置檔,但 FP32資料的峰值 FLOP/s翻倍,並且輸送量翻兩番,FP16同時使用相同的工藝技術 – 在能源效率方面令人印象深刻的成就

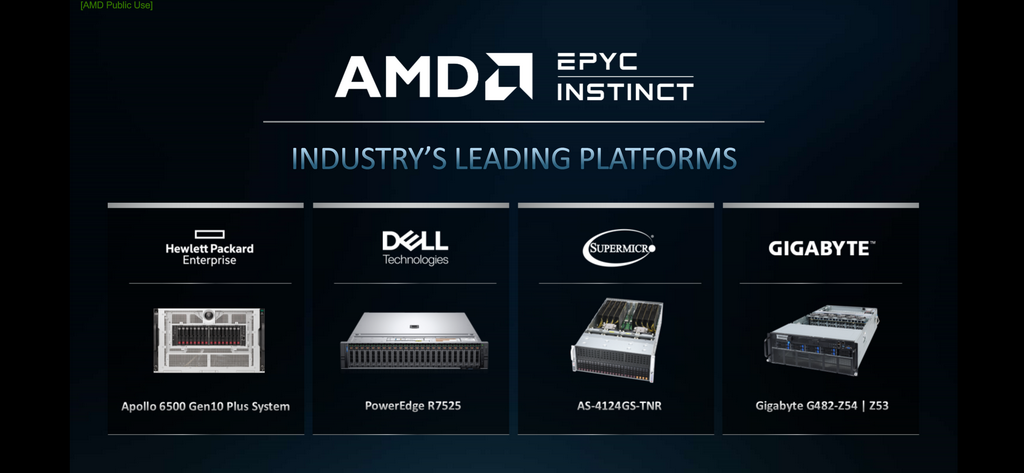

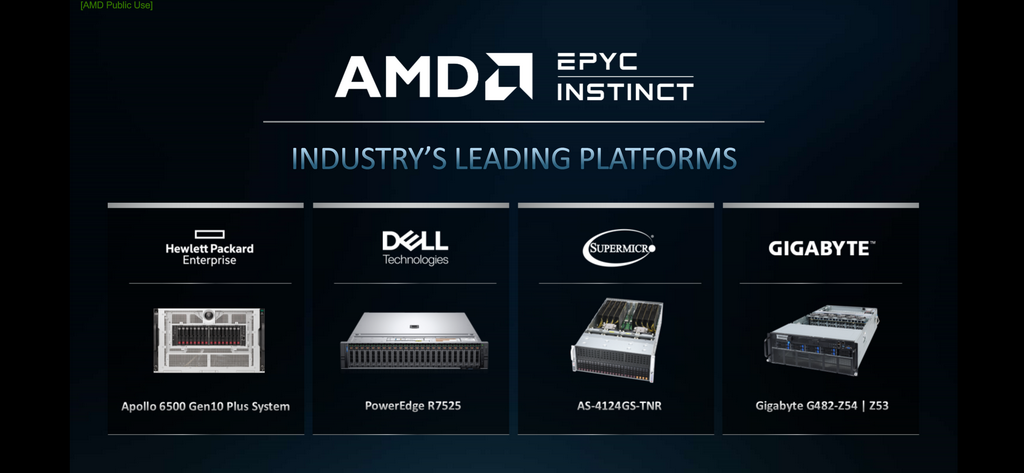

4家系統廠商均會在 11月發布

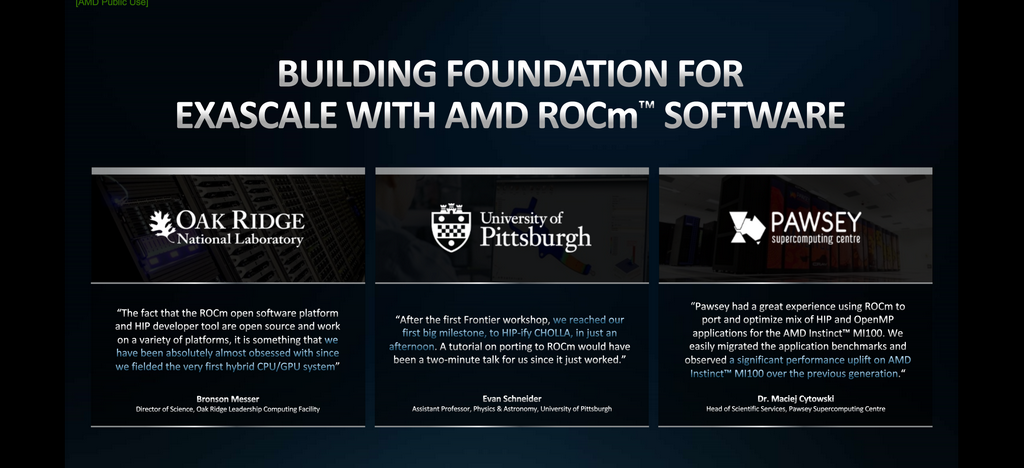

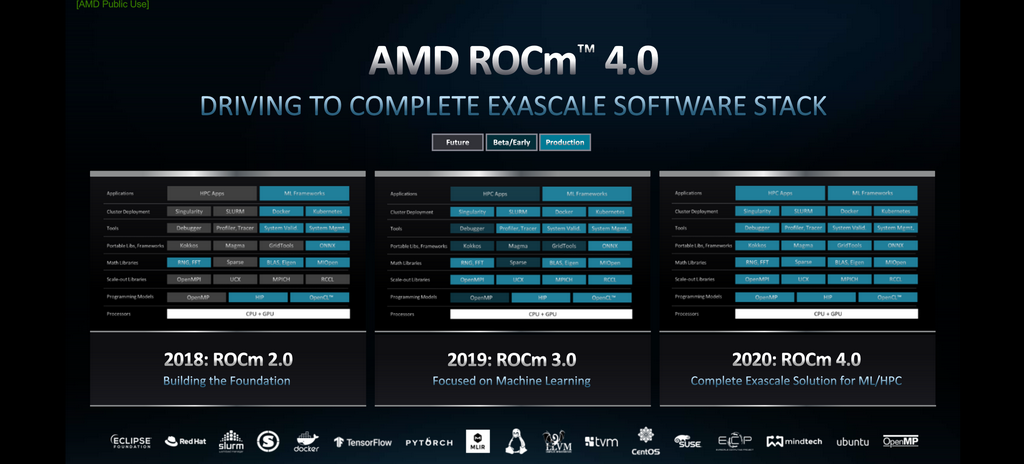

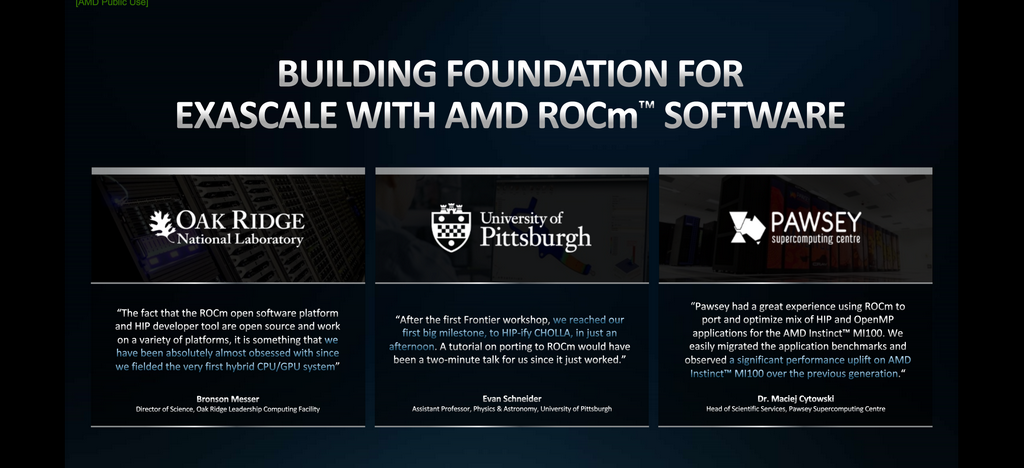

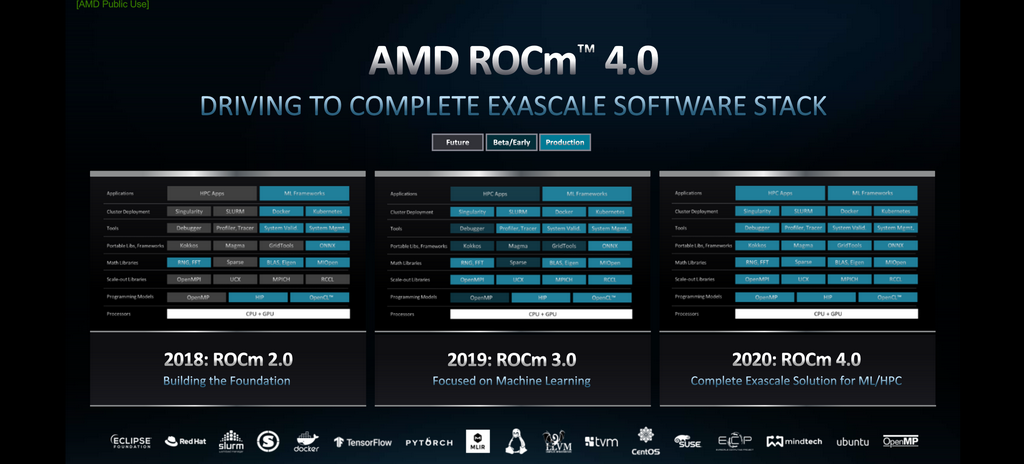

為了發展並支援各家開源廠商 AMD ROCm平台提供各項資源跟廠商使用,ROCm是第一個用於加快運算速度的開放原始碼超大規模級平台,並且該平台與程式設計語言無關,它提供了 UNIX選擇哲學,極簡主義和針對 GPU運算的模組化軟體開發, 您可以自由地為您的應用程式選擇甚至開發工具和語言執行時間,ROCm是為規模而構建的,它支援多 GPU運算,並具有豐富的系統執行時間,該系統執行時間具有許多大型應用程式、編譯器和語言執行時開發所需的關鍵功能

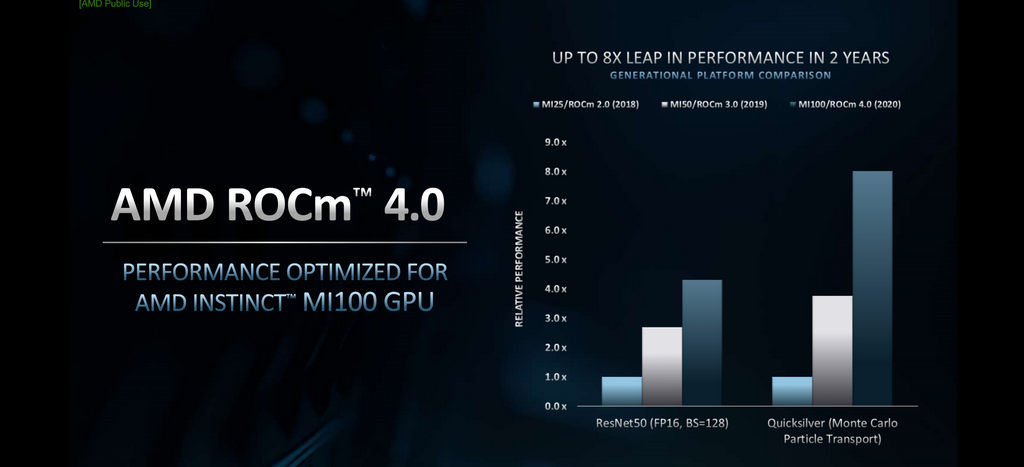

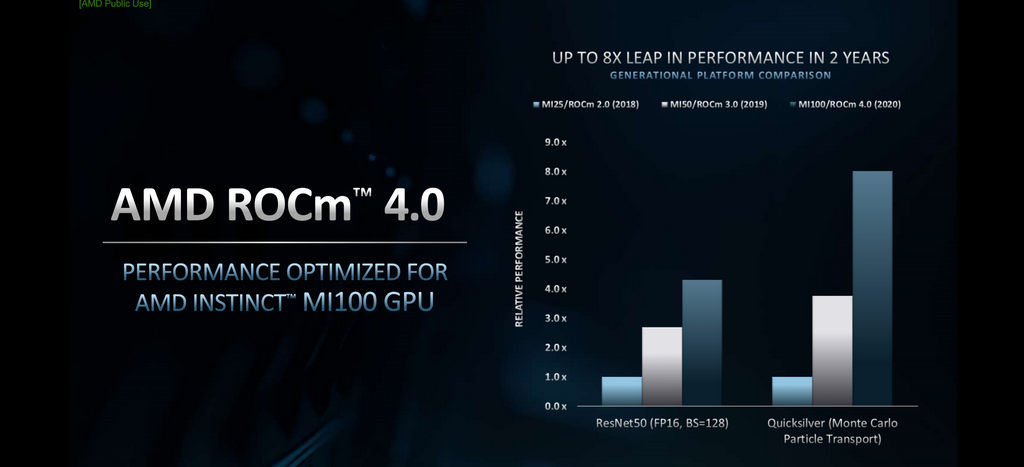

AMD ROCm 4.0可優化 Instinct MI100加速器用於加速運算的開放原始碼在 Exascale百萬兆級平台

Instinct MI100加速器融合人類本能與機器智慧,其設計從硬體的運算即採用開放方式, 並透過 Radeon開放計算平台 (ROCm) 軟體平台引入世界一流的 GPU技術和 Radeon Instinct開放資料中心設計生態系統方法,並憑藉各種系統架構支援和行業標準互連技術,實現更高水準的資料中心效能和效率,而 ROCm 4.0在 2年間更趨完善,亦為邁向 Exascale百萬兆級的最佳方案

眾多 AMD客戶群使用 Instinct MI100加速器以及 ROCm並反應良好

AMD Instinct M1100加速器

AMD Instinct MI100加速器是第一個 GPU加速器,其新型 AMD CDNA架構專為超大規模時代設計,基於新的 AMD CDNA架構構建,與第二代 AMD EPYC處理器配對時,用於 HPC和 Al的加速系統

AMD Instinct MI100加速器提供高達 11.5 T FLOPS的峰值 FP64性能為 HPC和高達 46.1TFLOPS峰值 FP32矩陣,Al和機器學習工作負載的性能,使用新的 AMD矩陣核心技術

AMD Instinct MI100加速器也為 Al培訓提供了近 7倍的 FP16理論峰值浮點性能提升

AMD針對在科學計算,結合 AMD ROCm開放軟體平臺,旨在為科學家和研究人員在 HPC中的工作提供卓越的基礎,並朝百萬兆級運算時代邁進

AMD Instinct MI100加速器性能諸元

AMD Instinct MI100加速器是新一代領頭之 HPC產品,擁有 7nm Vega架構的增強版本,亦為當前最新推出的加速器,在 GPU方面亦是 AMD CDNA組合中最重要的 HPC產品,支援生態系統無國界

第 2代 AMD EYPC之動量成長

第 2代 AMD EYPC擁有 64 Cores,4倍效能增長

HPC的負載是多元化的,並定位在多線程負載以滿足各在領域用戶的需求

CFX高頻處理器具有極高的運算性能跟上一代相比有提升 54%

3家廠商使用 AMD EPYC作生產及研究獲得很高的效益

在不同的工作負載上 AMD EPYC都能輕易的勝任

許多客戶成功案例,尤以 CGG、LUMI等最為出色

AMD正按計畫做第三代 EPYC OEM服務器之發布

20年來的 3個階段進程,將在 2025年達成 Exascale百萬兆級運算,Exascale百萬兆級運算指的是每秒可執行100萬兆次 (1 exaflops) 的運算,Exascale百萬兆級系統的效能可達現在最強大電腦的 50倍

AMD並改善了 GPU Peak Performance曲線成長趨緩的問題

AMD Instinct MI100加速器是針對高性能最快產品能實現超過 10TF資料處理,通過關鍵的優化和增強的可擴充性為數據中心提供動力

20年前的 ASCI與 2020年的 Instinct MI100加速器量體比較

GPU各個架構驅動不同用途負載比如高效能運算或在即時遊戲中各司其職

在過去的三十年中,圖形處理器已經從專門的固定功能架構發展成為完全可程式設計的架構加速器。雖然早期的設計側重於有限的計算,如照明轉換,今天的 CPU是通用的並交付了計算豐富的軟體,如應用程式和福特蘭 C++性能提升,行業同時演變為利用 CPU的關鍵領域,如機器學習和科學計算 – 這將推動創新幾十年在技術層面上,這轉化為硬體和軟體的兩大趨勢,首先,CPU已經從固定函數管道,以靈活的計算引擎,如 GCN架構,提供標量和向量處理。同時軟體生態系統已迅速擴展,通過提供關鍵工具,包括從數學庫和編譯器到調試器,到群集管理和部署,一切

AMD為從 PC遊戲玩家到數據中心平臺等廣泛的用例構建高性能計算解決方案,而傳統的 CPU被構建為一般用途,旨在推動面向圖形和面向計算的工作負載,AMD最近推出了一種不同的方法來提高效率,現在有兩種架構:AMD RDNA針對遊戲進行了優化,以最大化每秒幀數,AMD CDNA針對計算進行了優化,以突破每秒 flops的限制

AMD CDNA架構

CDNA的主要重點是增強數據中心的效能、效率、功能和可擴充性,藉助 CDNA,AMD將創建專門針對高性能計算,機器學習和 HPC優化的GPU,首款採用 CDNA架構之產品 2X運算單元 AI FP16 PCIe 4.0 4X頻寬,記憶體頻寬達 1.2TB/s

AMD Instinct MI100加速器在 for HPC & AI單雙精度運算性能比較上,AMD Instinct MI100加速器可實現百億億次級以上的雙精度處理能力

AMD Instinct MI100加速器在 Open Souce之各工作負載上的表現

生物研究團隊研究蛋白質工程以產生新的產業,設計新的藥物和醫學療法來改善人類的生活,氣候科學家並藉此模擬世界海洋與大氣的行為,建立氣候急劇變化的模型,幫助我們瞭解我們需要做些什麼來使地球一直作為一個適宜生存和舒適的地方,科學家正在以盡可能小的規模研究材料的性質,從發電與輸電到生產速度更快、體積更小、功能更多的計算機和儲存裝置

使用 AMD Infinity結構改進 HPC和 Al性能

AMD CDNA架構計算單元

命令處理器和調度邏輯將更高級別的 API命令轉換為計算任務,這些計算任務反過來以計算陣列方式實現,並由非同步計算引擎 (ACE) 管理,四個 (ACE) 中每個都維護獨立的命令流,可以向計算單元調度

AMD CDNA架構的令人印象深刻的 120個 Cus,被組織成四個 CUs陣列,CUs派生自較早的 GCN體系結構和執行包含 64個工作項目,但是,使用新的矩陣核心引擎來增強針對執行對矩陣數據類型進行操作的計算內核進行了優化,提高了計算輸送量和能效

經典的 GCN計算內核包含針對標量和向量指令優化的各種管道,特別是每個 CU包含標量寄存器檔、標量執行單元和標量數據緩存,用於處理跨波前共用的指令,例如常見的控制邏輯或位址計算。同樣 4個向量執行單元也包含一個大型向量寄存器檔,針對 FP32和向量數據緩存進行了優化,通常,向量管道為 16-wide,每個 64-wide的 wavefront在四個週期

AMD CDNA架構基於 GCN的標量和向量基礎,並增加了矩陣作為一流的陣容,而同時為機器學習的新數位格式添加支援,並保留任何軟體的向後相容性

為 GCN架構編寫這些矩陣核心引擎增加了一個新的指令系列,矩陣融合乘法-添加或 MFMA系列執行混合精度術,並使用五種不同類型的輸入在 KxN矩陣上操作

數據: 4bit整數(INT4)、8bit整數 (INT8)、16bit半精度 FP (FP16)、16bit brain FP (bf16) 和 32bit單精度 (FP32)

所有 MFMA指令都會生成 32bit整數 (INT32) 或 FP32輸出,從而降低最終輸出期間溢出的可能性矩陣乘法的累積階段

不同的數位格式都有不同的推薦應用。業界普遍認為,INT8數位是主要用於具有量化權重或數據的 ML推理,並且具有最佳輸送量和最低記憶體使用量。相比之下,大多數 ML訓練和某些 HPC應用程式預設使用 IEEE FP32資料,其中 8bit分配給指數範圍和 23bit用於捕獲精度的尾數,FP16是另一個 IEEE標準,專為圖形工作負載而設計,使用 5bit指數和 10bit,雖然 FP16比 FP32 效率更高,但縮小的範圍並不總是開箱即用,對於 ML訓練有時需要調整演演演算法以避免溢出和收斂問題

120個增強型計算單元 (CUs) 建立在 GCN架構的基礎上,並組織成四個計算引擎,以及負責 AMD Instinct MI100加速器中的所有計算,雖然受到上一代 CCN架構的啟發,但每個 CU使用矩陣核心引擎進行重新設計並增強,可顯著提高多種不同的數位的計算輸送量格式。在所有 CU中,Instinct MI100加速器可以實現理論雙精度浮點輸送量高達 11.5TFLOP/s – 第一個打破 10TFLOP/s障礙的處理器。不像面向圖形的 AMD RDNA系列,AMD CDNA系列移除所有旨在加速圖形任務的固定功能硬體,如閘格化、細分、圖形快取、混合,甚至顯示引擎,但是,AMD CDNA系列保留了 HEVC、H.264和 VP9解碼的專用邏輯,即有時用於對多媒體數據進行操作的計算工作負載,例如用於物件檢測的機器學習?刪除固定功能圖形硬體可釋放面積和動力,以投資額外的計算單元,從而提高性能和效率

L2 Cache和記憶體

AMD Instinct MI100加速器記憶體層次結構的最低級別位於 CUs,但大多數科學或機器內學習數據集以千兆位元組或 TB為單位進行測量,並快速溢出到記憶體中,記憶體層次結構負責持有工作數據,並有效地將數據傳遞到計算中消耗數據的計算陣列

L2 Cache在整個晶元中共用,並物理分區為多個切片。對於 Instinct MI100加速器,Cache為 16way設置-關聯,包括 32個切片(是 MI50的兩倍),總容量為 8MB,每個切片可以維持 128B超過 6TB/s的 CPU聚合頻寬

AMD CDNA架構針對要求最苛刻的工作負載而設計,記憶體控制器和介面專為最大頻寬、能效和極高的可靠性,記憶體控制器驅動 4或 8個的共同封裝 HBM2堆疊為 2.4CT/s,理論輸送量為 1.23TB/s ,比上一代 AMD加速器快 20%,同時保持 CPU功率預算常數。HBM2記憶體的 32GB受強大的 ECC保護,使關鍵任務應用程式能夠大規模運作

溝通和擴展

系統體系結構的最後一部分是通信,以跨多個 CPU進行擴展。雖然運行小型工作負載的系統可能使用單個 AMD Instinct MI100加速器, 更大和更苛刻的問題, 如訓練神經網路需要更強大系統,例如,用於語言建模的 BERT神經網路可擴展到最多數千個處理器最近的 MLPerf Benchmark AMD CDNA架構使用基於標準的高速 AMD無限交換矩陣技術連接到其他 CPU Infinity fabric鏈路以 23CT/s 運行,與上一代鏈路寬 16bit,但 MI100帶來了第三個鏈路,用於在四 CPU配置提供更大的雙節頻寬,並支援高度可擴展的系統,與 PCIe不同,AMD Infinity Fabric連結支援一致的 CPU記憶體,使多個 CPU能夠共用一個位址空間,並在單個問題上緊密配合

利用新的矩陣引擎增強節能

與 GCN中的傳統向量管道相比,矩陣執行單元具有若干優勢

第一:執行單元減少寄存器檔讀取的數量,因為在矩陣乘法中,會重新使用許多輸入值

第二:較窄的數據類型為不需要完全 FP32精度的工作負載(例如機器學習)創造了巨大的機會,一般來說,能量乘積操作消耗的是輸入數據類型的平方,因此從 FP32到 FP16或 bf16的轉換可以節省巨大的能量

MI100和 MI50之間的數位格式和峰值輸送量的代際比較

對向量執行單元執行矩陣操作,上表描述了使用傳統向量指令和新的矩陣乘法指令在 MI50與 MI100的比較,新指令和執行資源的最終結果是對於矩陣計算,MI100保持與上一代類似的功率配置檔,但 FP32資料的峰值 FLOP/s翻倍,並且輸送量翻兩番,FP16同時使用相同的工藝技術 – 在能源效率方面令人印象深刻的成就

4家系統廠商均會在 11月發布

為了發展並支援各家開源廠商 AMD ROCm平台提供各項資源跟廠商使用,ROCm是第一個用於加快運算速度的開放原始碼超大規模級平台,並且該平台與程式設計語言無關,它提供了 UNIX選擇哲學,極簡主義和針對 GPU運算的模組化軟體開發, 您可以自由地為您的應用程式選擇甚至開發工具和語言執行時間,ROCm是為規模而構建的,它支援多 GPU運算,並具有豐富的系統執行時間,該系統執行時間具有許多大型應用程式、編譯器和語言執行時開發所需的關鍵功能

AMD ROCm 4.0可優化 Instinct MI100加速器用於加速運算的開放原始碼在 Exascale百萬兆級平台

Instinct MI100加速器融合人類本能與機器智慧,其設計從硬體的運算即採用開放方式, 並透過 Radeon開放計算平台 (ROCm) 軟體平台引入世界一流的 GPU技術和 Radeon Instinct開放資料中心設計生態系統方法,並憑藉各種系統架構支援和行業標準互連技術,實現更高水準的資料中心效能和效率,而 ROCm 4.0在 2年間更趨完善,亦為邁向 Exascale百萬兆級的最佳方案

眾多 AMD客戶群使用 Instinct MI100加速器以及 ROCm並反應良好