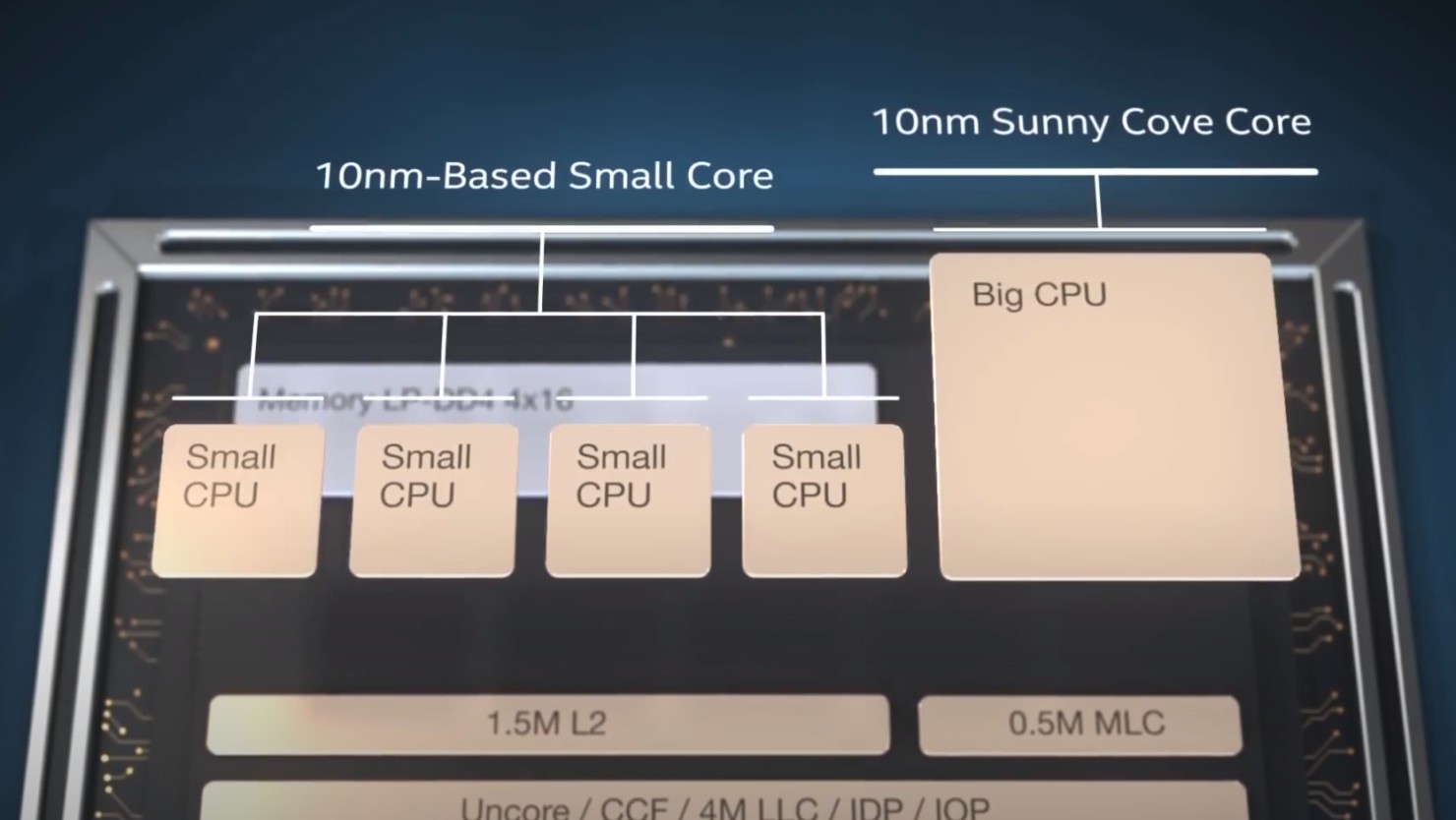

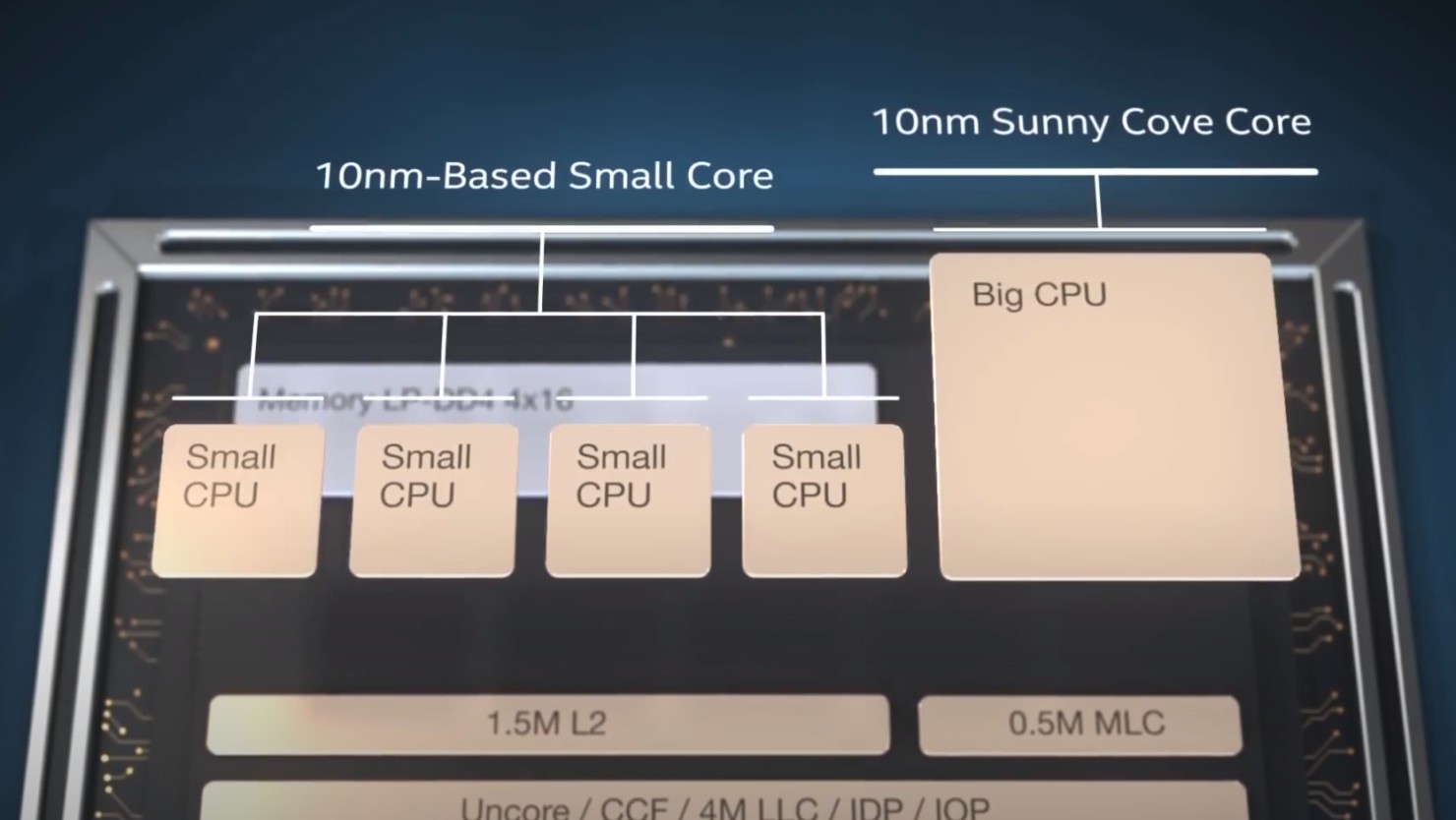

Intel 在2021年推出了首款採用大小核混合架構的 Alder Lake 處理器,本身與前一代的 Rocket Lake 一樣,都支援 AVX -256 和 AVX-512 指令集。不過基於多方面因素考慮,最終強制禁用了 AVX-512,不但讓晶片失去了一項特性,而且浪費了寶貴的晶片面積,直到現在的 Raptor Lake 也不支援。反觀競爭對手 AMD,基於 Zen 4 架構的 Ryzen 7000 系列則完全支援 AVX-512 指令集,使其在某些特定工作負載中有更好的性能表現。

今天 Intel 發布了新的高級性能擴充指令集(APX),並揭露了 AVX10 指令集架構,這將首次讓 P-Core 和 E-Core 同時支援 AVX-512 指令集,解決了 Alder Lake 和 Raptor Lake 上遇到的問題。其具備 AVX-512 指令集的所有功能,適用於具有 256bit 和 512bit 矢量寄存器的處理器。不過 AVX10 指令集架構並不支援當前處理器,而是用於未來的晶片,並適用消費級和伺服器處理器。

作為全新高級性能擴充指令集的一部分,AVX10 指令集架構提供了:

– 可選512-bit FP/int

– 128/256-bit FP/int

– 32個矢量寄存器

– 8個掩碼寄存器

– 256/512-bit嵌入式捨入

– 嵌入式廣播

– Scalar/SSE/AVX "promotions"

– 本地媒體添加

– HPC 新增功能

– Gather/Scatter

– Transcendental support

– Version-based enumeration

– 支援 P-Core 和 E-Core

AVX10 指令集架構有兩個版本,分別為 AVX10.1 和 AVX10.2,前者只支援 P-Core,後者增加了對 E-Core 的支援,其中還包括 256bit 矢量長度和其他新功能。簡單來說,P-Core 可以使用 512bit 矢量長度運行,而 E-Core 以 256bit 模擬運行,類似於 Arm 的 SVE(可伸縮矢量擴展)指令集。

Intel 將會從 Granite Rapids 開始支援 AVX10 指令集架構首個版本,也就是 AVX10.1,開始從 AVX-512 向 AVX10 過渡。

來源

今天 Intel 發布了新的高級性能擴充指令集(APX),並揭露了 AVX10 指令集架構,這將首次讓 P-Core 和 E-Core 同時支援 AVX-512 指令集,解決了 Alder Lake 和 Raptor Lake 上遇到的問題。其具備 AVX-512 指令集的所有功能,適用於具有 256bit 和 512bit 矢量寄存器的處理器。不過 AVX10 指令集架構並不支援當前處理器,而是用於未來的晶片,並適用消費級和伺服器處理器。

作為全新高級性能擴充指令集的一部分,AVX10 指令集架構提供了:

– 可選512-bit FP/int

– 128/256-bit FP/int

– 32個矢量寄存器

– 8個掩碼寄存器

– 256/512-bit嵌入式捨入

– 嵌入式廣播

– Scalar/SSE/AVX "promotions"

– 本地媒體添加

– HPC 新增功能

– Gather/Scatter

– Transcendental support

– Version-based enumeration

– 支援 P-Core 和 E-Core

AVX10 指令集架構有兩個版本,分別為 AVX10.1 和 AVX10.2,前者只支援 P-Core,後者增加了對 E-Core 的支援,其中還包括 256bit 矢量長度和其他新功能。簡單來說,P-Core 可以使用 512bit 矢量長度運行,而 E-Core 以 256bit 模擬運行,類似於 Arm 的 SVE(可伸縮矢量擴展)指令集。

Intel 將會從 Granite Rapids 開始支援 AVX10 指令集架構首個版本,也就是 AVX10.1,開始從 AVX-512 向 AVX10 過渡。

來源