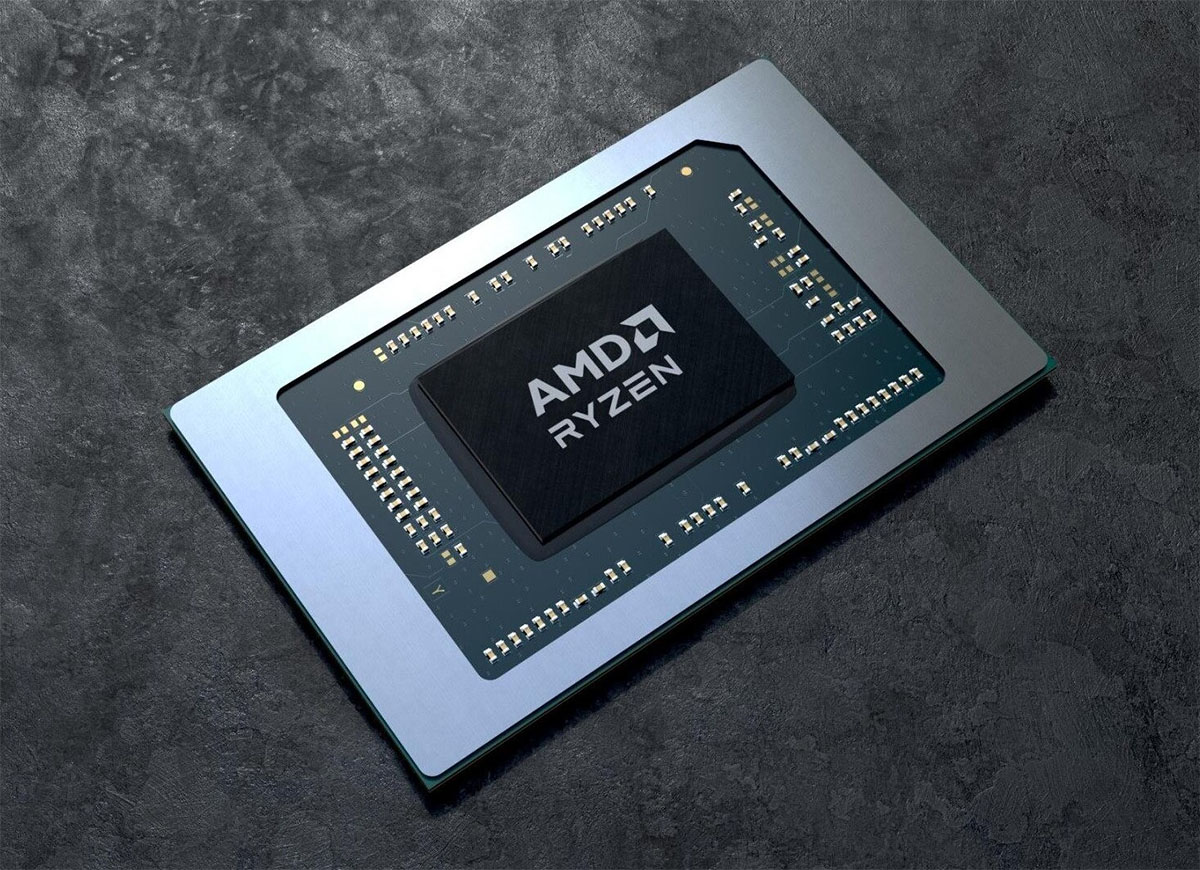

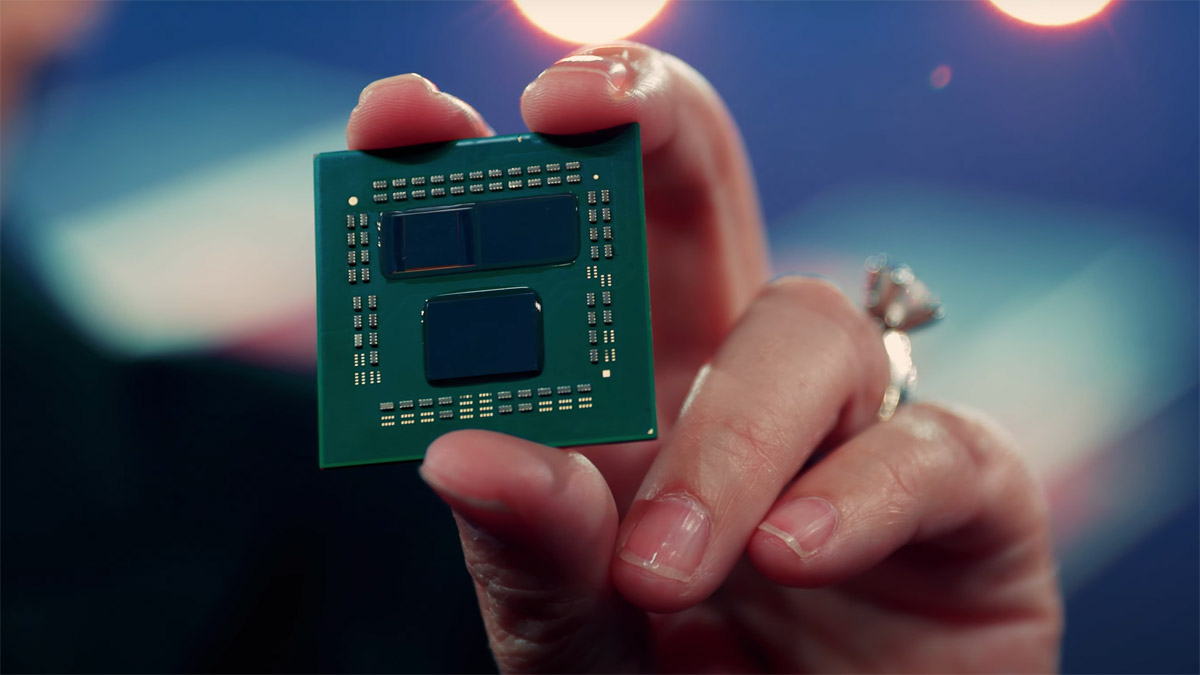

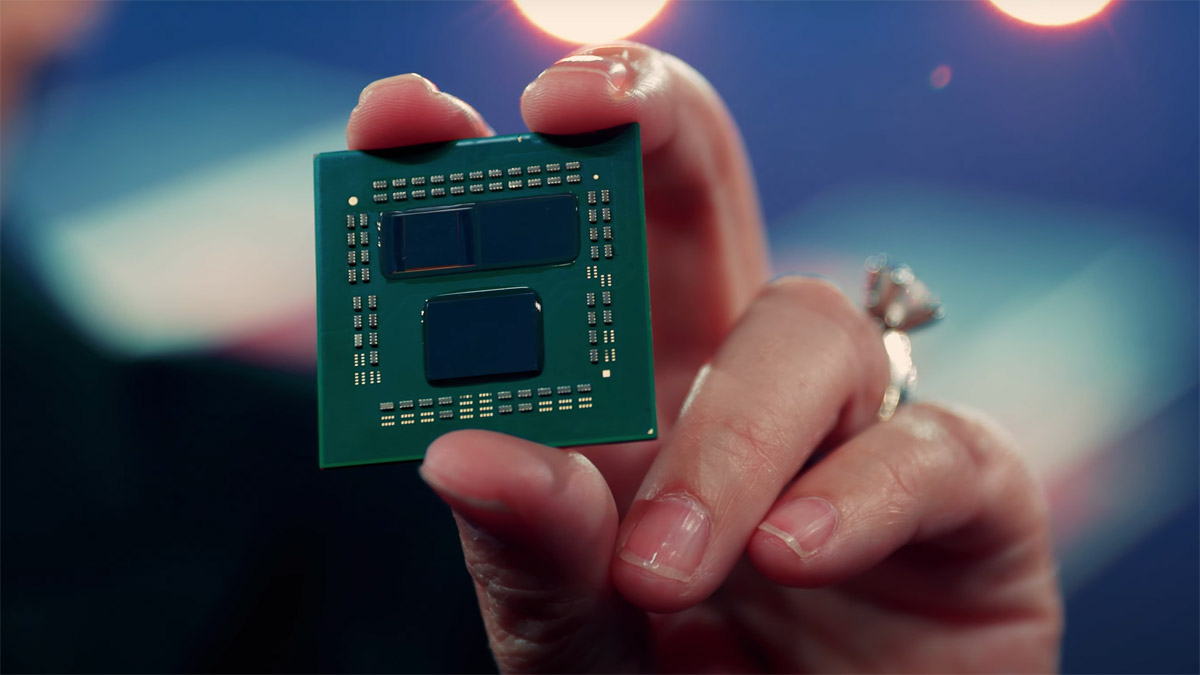

今年 Computex 2021 上,AMD CEO 蘇姿丰展示了採用 3D 垂直快取(3D V-Cache)技術的 Zen 3 架構桌面處理器。這項創新的技術可以為每個 CCD 帶來額外的 64MB 7nm SRAM 快取,使得處理器的 L3 快取容量由 32MB 增加到 96MB,容量增加到原來的三倍。

近日,高級技術研究員 Yuzo Fukuzaki 發表了一篇文章,主要說明 AMD 這項技術在處理器快取層結構中的最合理位置,顯然通過 3D 垂直快取技術,可以擴展處理器的 L3 快取,而不是作為所謂“L4快取”使用,而16核心的 Ryzen 9 5950X 處理器共擁有 192MB 的 L3 快取。

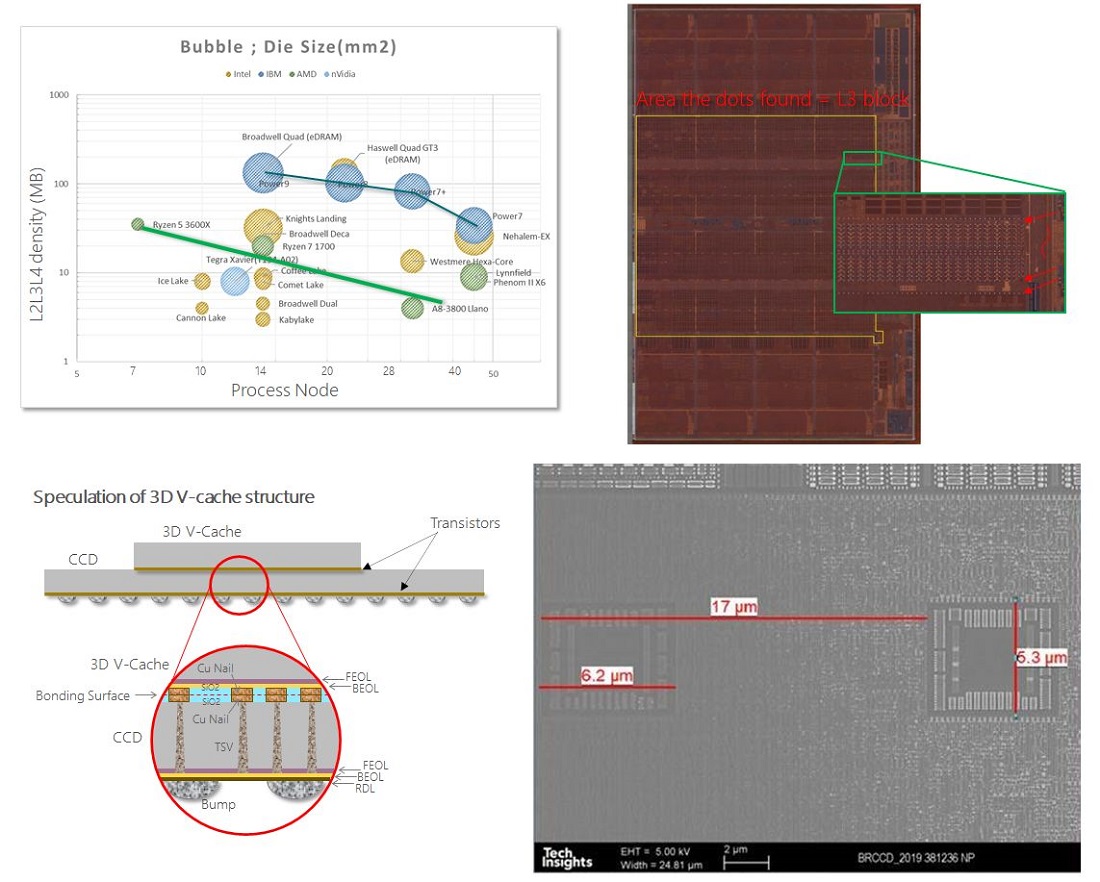

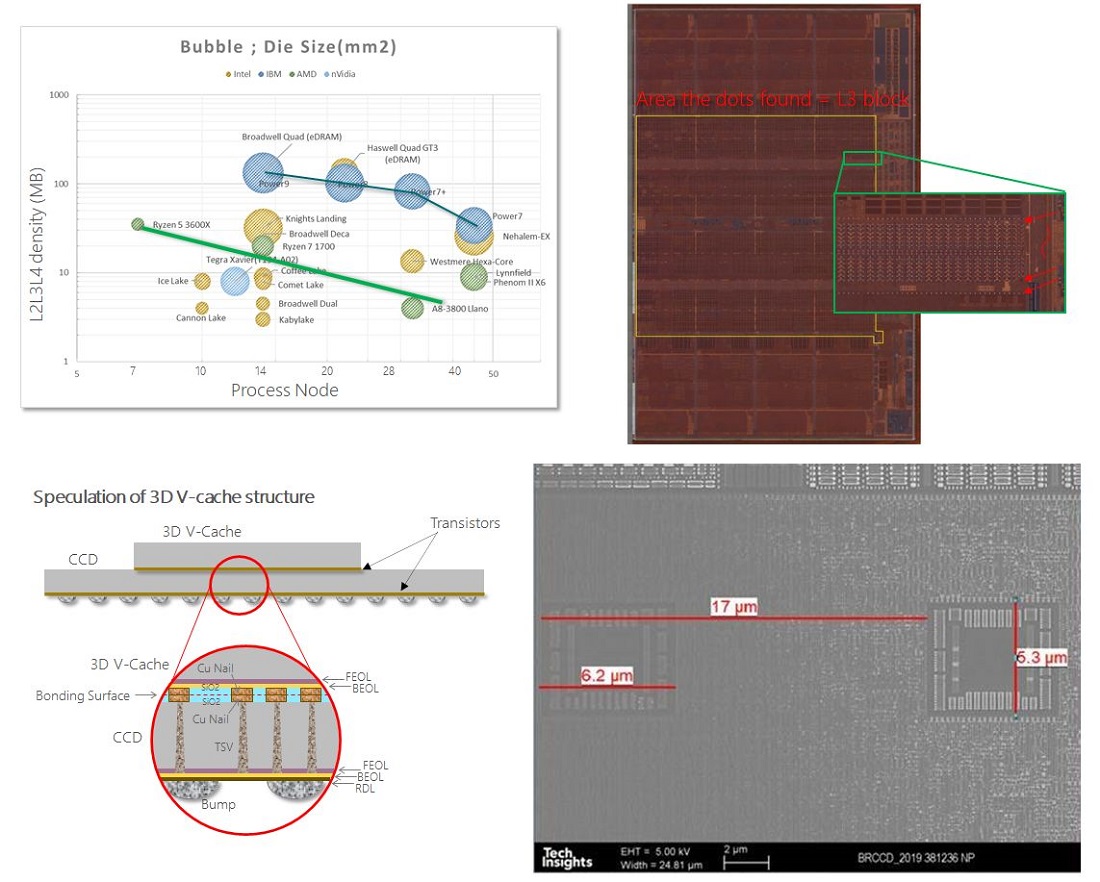

SRAM 晶片 3D 垂直快取採用了 7nm 製程製造,尺寸為6×6 m㎡。據推測,3D 垂直快取晶片大約有2300個矽通孔(TSV),單孔直徑約17μm,讓底層 CCX 與 3D 垂直快取晶片緊密相連。Zen 3 架構處理器應該在設計之初就考慮到使用 3D 垂直快取晶片的可能性,這說明 AMD 在該技術上已開發多年。

根據此前 AMD 的官方介紹,3D 垂直快取技術是基於台積電的 SoIC 技術。作為一種無損晶片堆疊技術,意味著不使用微凸點或焊料來連接兩個晶片,兩個晶片被銑成一個完美的平面。底層 CCX 與頂層 L3 快取之間是一個完美的對齊,矽通孔可以在沒有任何類型的粘合材料的情況下進行匹配。

其 CCX 做了翻轉(由面向頂部改為面向底部)處理,然後削去了頂部95%的矽,再將 3D 垂直快取晶片安裝在上面,讓快取和核心之間的距離縮短了1000倍,減少了發熱、功耗和延遲。

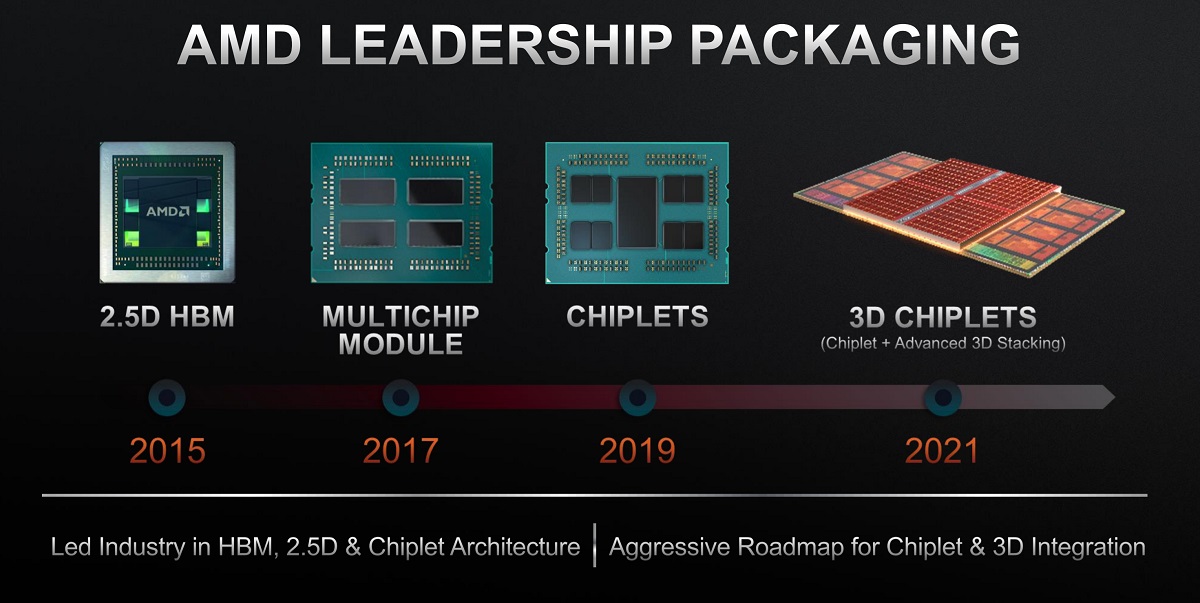

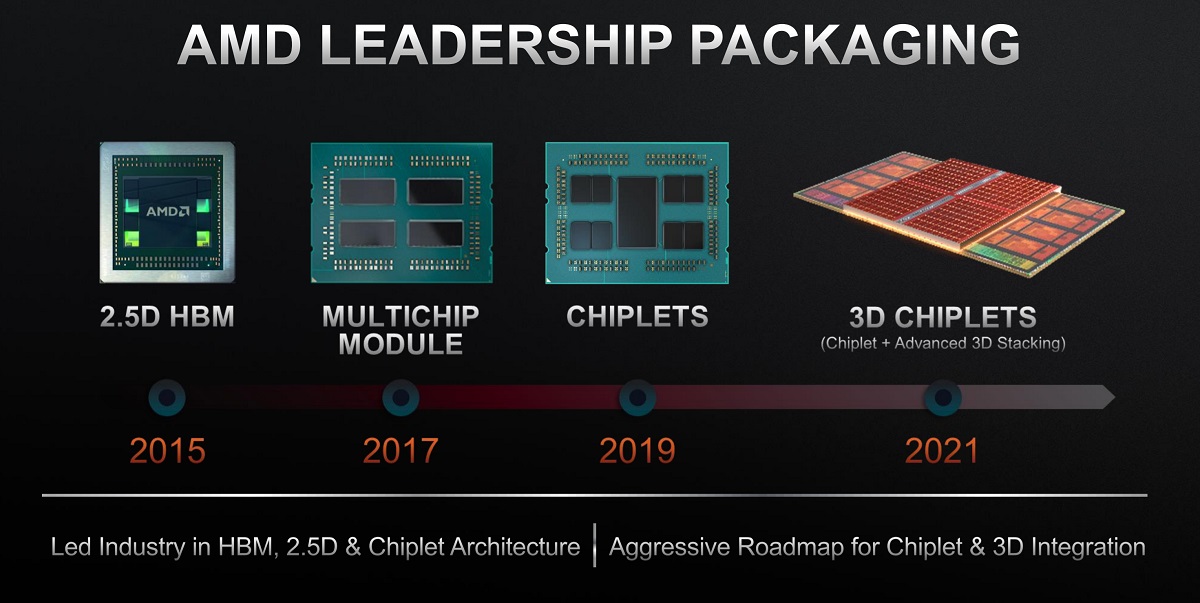

Yuzo Fukuzaki 表示,為了應對 Memory Wall(記憶體牆)問題,處理器的快取設計非常重要。更大容量的快取在高階處理器上早已成為一種趨勢,而 3D 垂直快取技術有助於提供處理器的性能,同時可以解決低良品率問題,更好控制成本。

來源

近日,高級技術研究員 Yuzo Fukuzaki 發表了一篇文章,主要說明 AMD 這項技術在處理器快取層結構中的最合理位置,顯然通過 3D 垂直快取技術,可以擴展處理器的 L3 快取,而不是作為所謂“L4快取”使用,而16核心的 Ryzen 9 5950X 處理器共擁有 192MB 的 L3 快取。

SRAM 晶片 3D 垂直快取採用了 7nm 製程製造,尺寸為6×6 m㎡。據推測,3D 垂直快取晶片大約有2300個矽通孔(TSV),單孔直徑約17μm,讓底層 CCX 與 3D 垂直快取晶片緊密相連。Zen 3 架構處理器應該在設計之初就考慮到使用 3D 垂直快取晶片的可能性,這說明 AMD 在該技術上已開發多年。

根據此前 AMD 的官方介紹,3D 垂直快取技術是基於台積電的 SoIC 技術。作為一種無損晶片堆疊技術,意味著不使用微凸點或焊料來連接兩個晶片,兩個晶片被銑成一個完美的平面。底層 CCX 與頂層 L3 快取之間是一個完美的對齊,矽通孔可以在沒有任何類型的粘合材料的情況下進行匹配。

其 CCX 做了翻轉(由面向頂部改為面向底部)處理,然後削去了頂部95%的矽,再將 3D 垂直快取晶片安裝在上面,讓快取和核心之間的距離縮短了1000倍,減少了發熱、功耗和延遲。

Yuzo Fukuzaki 表示,為了應對 Memory Wall(記憶體牆)問題,處理器的快取設計非常重要。更大容量的快取在高階處理器上早已成為一種趨勢,而 3D 垂直快取技術有助於提供處理器的性能,同時可以解決低良品率問題,更好控制成本。

來源