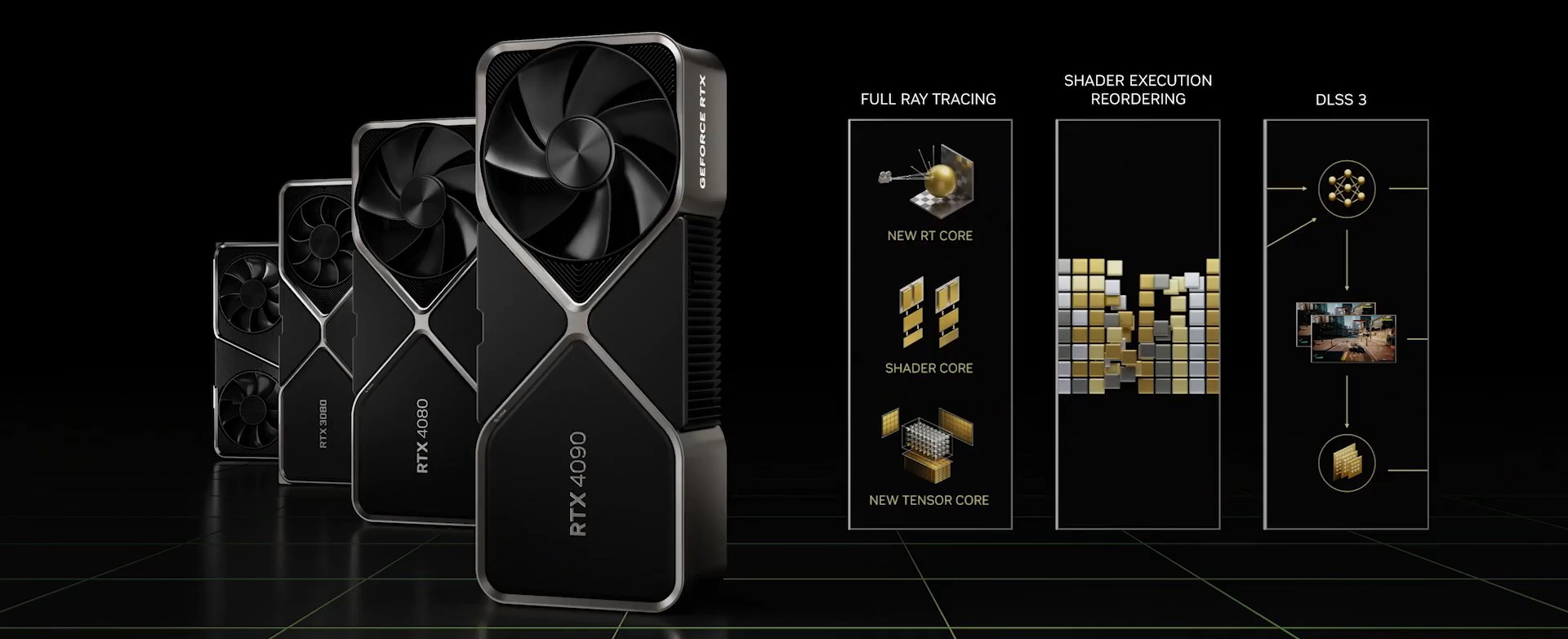

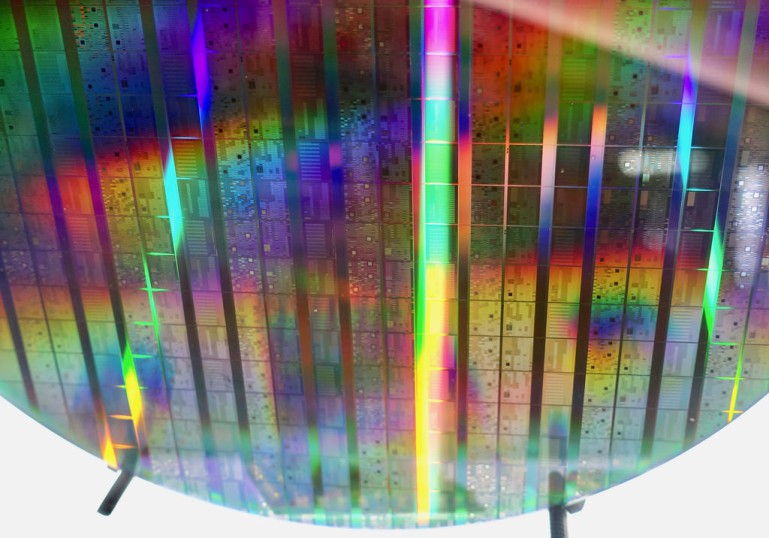

台積電在不久前的 TSMC Technology Symposium 技術會議上,提出了具有革命性意義的製程技術 Wafer-on-Wafer(WoW,堆疊晶圓) ,就像是 3D NAND 記憶體多層堆疊一樣,將兩層Die以鏡像方式垂直堆疊起來,有望用於生產顯卡 GPU,創造出晶體管規模更大 GPU。

此前台積電已經研發出相類似的技術 Chip on Wafer on Substrate(CoWoS)、Integrated Fan-Out (InFO),這兩種技術目前已經應用在多種產品上,比方說Intel 和 Xilinx 的 FPGA 晶片應用了 CoWos ,蘋果的A系列 SoC 應用了InFO。而這一次的 WoW 最大應用將可能會在 GPU 核心上,可以在不增加 GPU 核心面積或者是使用更小製程下增加晶體管數量,從而提升顯卡效能。

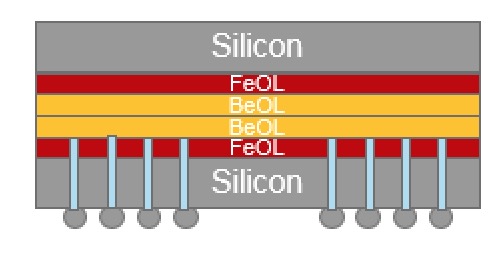

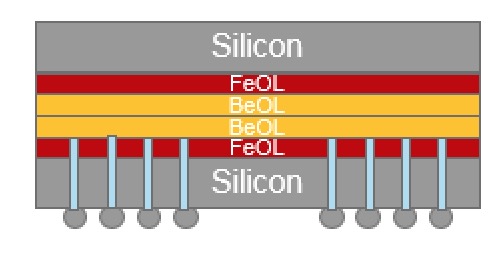

根據著名 EDA 大廠 Cadence 的博客描述,WoW 技術通過10μm的矽穿孔方式連接上下兩塊 die,這樣一來可以在垂直方向上堆疊更多 die,也意味著 die 之間的延遲通信及大地減少,引入更多地核心。

不過目前 WoW 技術最大問題就是對於製程要求非常高,die 之間要準確無誤地對齊,而且確保任何一片 die 都是沒有問題的,否則組裝完成後發現其中一個工作不了,整個封裝完成的晶片就報廢了,因此良品率比較低,生產成本較高。所以在已經非常成熟的16nm上加入 WoW 是比較妥當,但台積電目標確實在未來的 7 / 5nm 上應用。

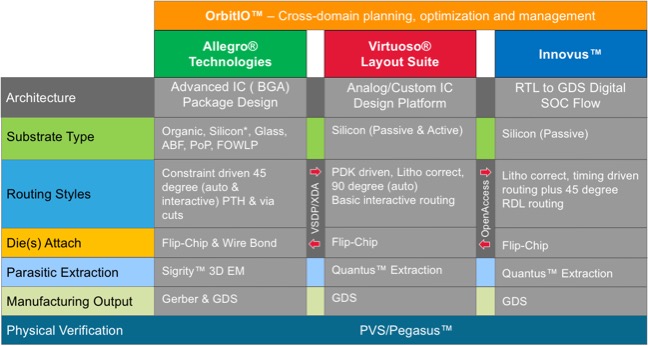

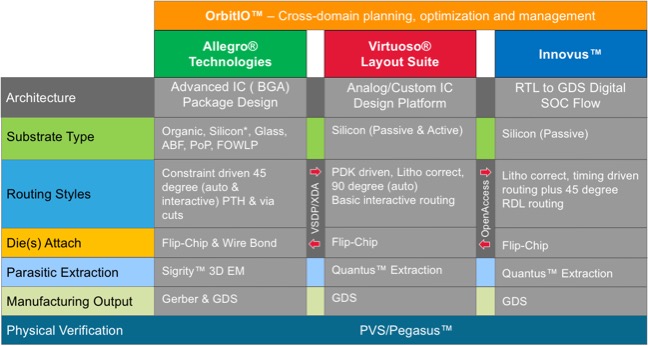

目前 Cadence 和台積電宣佈在 Cadence 工具中已通過 WoW Reference Flow 1.0 標準認證。

來源:

https://community.cadence.com/cadence_blogs_8/b/breakfast-bytes/posts/tsmc-placeholder

http://www.expreview.com/61044.html

此前台積電已經研發出相類似的技術 Chip on Wafer on Substrate(CoWoS)、Integrated Fan-Out (InFO),這兩種技術目前已經應用在多種產品上,比方說Intel 和 Xilinx 的 FPGA 晶片應用了 CoWos ,蘋果的A系列 SoC 應用了InFO。而這一次的 WoW 最大應用將可能會在 GPU 核心上,可以在不增加 GPU 核心面積或者是使用更小製程下增加晶體管數量,從而提升顯卡效能。

根據著名 EDA 大廠 Cadence 的博客描述,WoW 技術通過10μm的矽穿孔方式連接上下兩塊 die,這樣一來可以在垂直方向上堆疊更多 die,也意味著 die 之間的延遲通信及大地減少,引入更多地核心。

不過目前 WoW 技術最大問題就是對於製程要求非常高,die 之間要準確無誤地對齊,而且確保任何一片 die 都是沒有問題的,否則組裝完成後發現其中一個工作不了,整個封裝完成的晶片就報廢了,因此良品率比較低,生產成本較高。所以在已經非常成熟的16nm上加入 WoW 是比較妥當,但台積電目標確實在未來的 7 / 5nm 上應用。

目前 Cadence 和台積電宣佈在 Cadence 工具中已通過 WoW Reference Flow 1.0 標準認證。

來源:

https://community.cadence.com/cadence_blogs_8/b/breakfast-bytes/posts/tsmc-placeholder

http://www.expreview.com/61044.html