2020年架構日揭曉了Willow Cove、Tiger Lake和Xe架構的相關訊息,並隨著六大創新支柱的發展而推出了全新電晶體技術

2020年8月13日 – 英特爾首席架構師 Raja Koduri、英特爾院士及其架構師團隊,詳細介紹了英特爾在科技六大創新支柱上所取得的進展。英特爾揭示其10奈米SuperFin技術,代表了公司歷史上最大的單一節點內升級功能,提供等同於轉換至全新製程節點技術的效能改進。

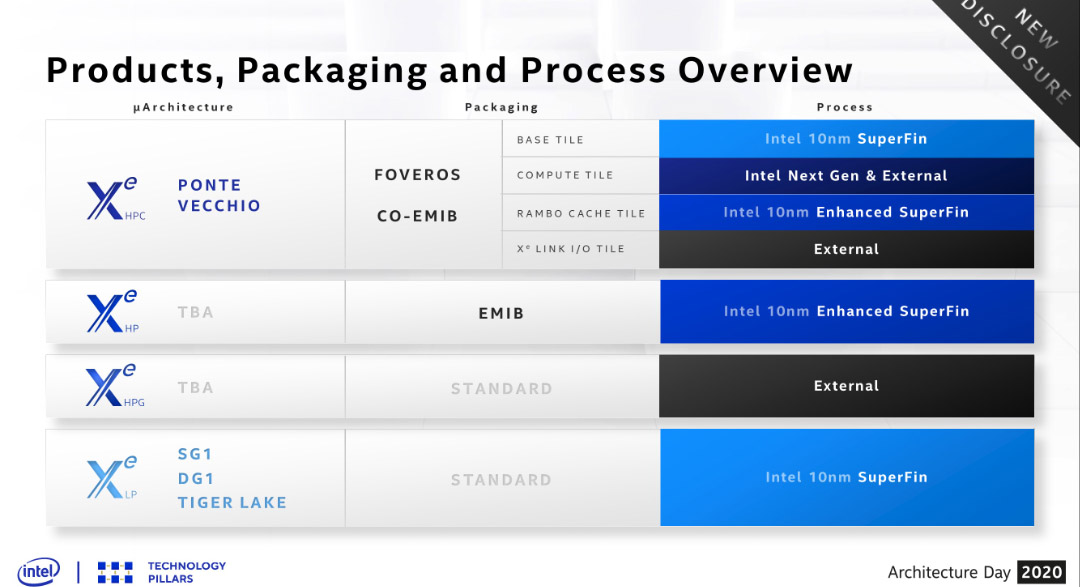

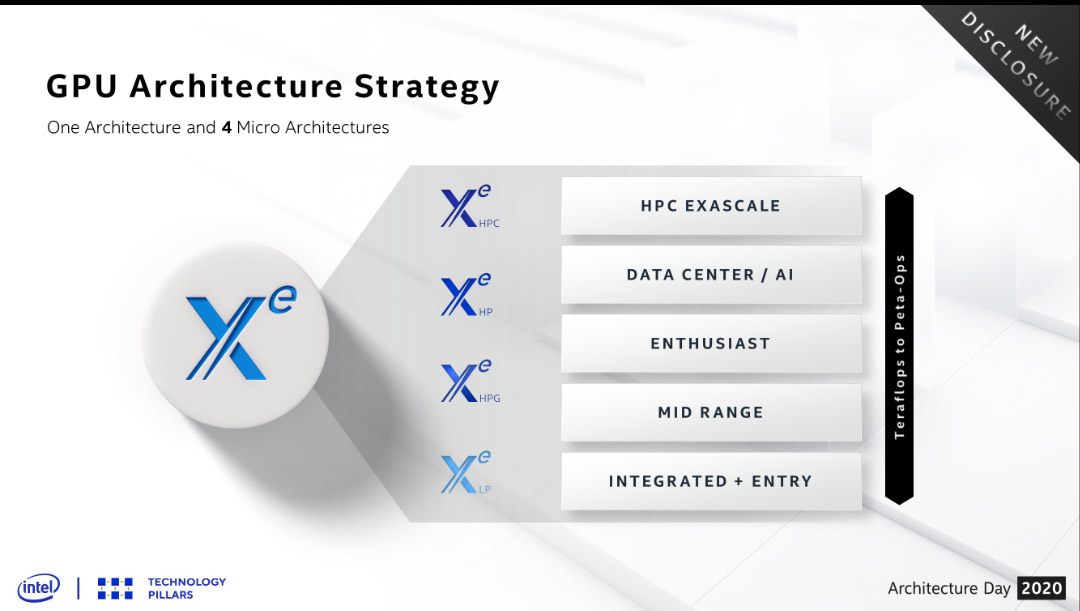

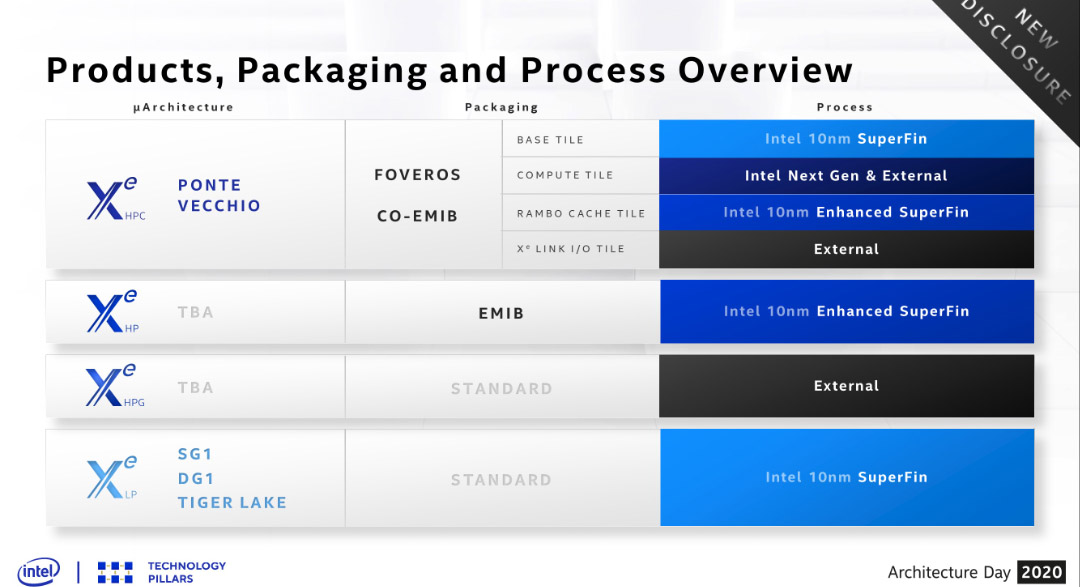

英特爾公司還公佈Willow Cove微架構和針對行動客戶端的Tiger Lake 系統單晶片架構的詳細資訊,並首度揭示了其完全可擴展的Xe繪圖架構,這些架構可滿足從消費端至高效能運算,再到遊戲用途的各個市場。英特爾將其解藕晶片設計方式、結合先進的封裝技術,XPU產品和以軟體為中心的策略,致力為客戶提供領先效能的全方位解決方案。

10奈米 SuperFin 技術

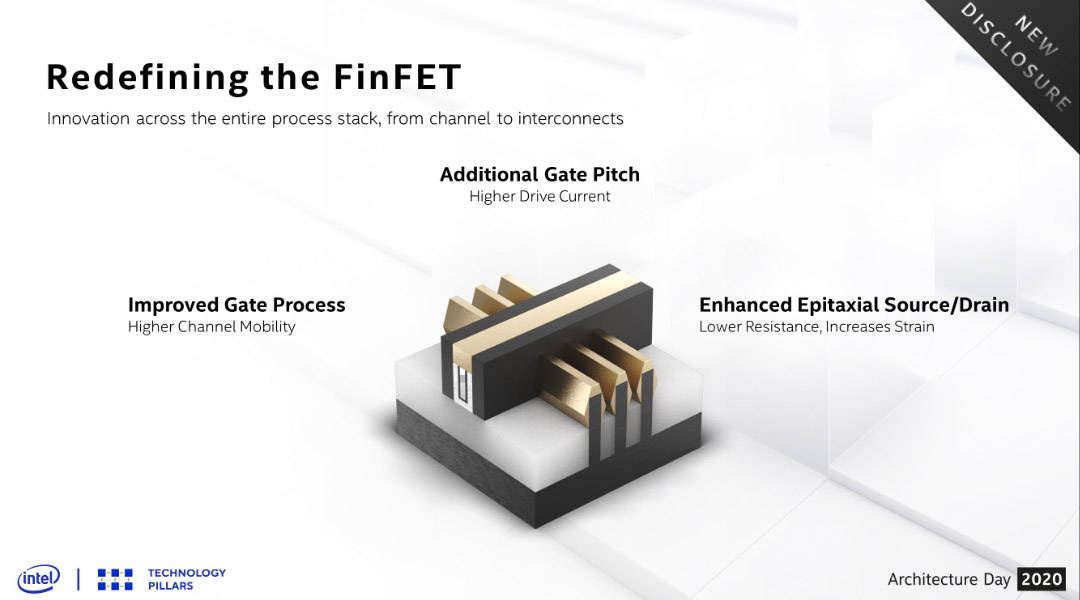

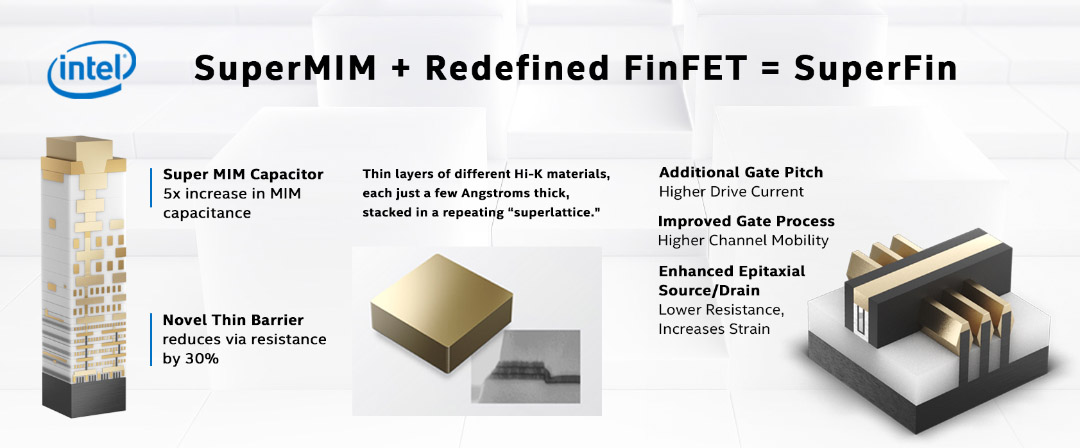

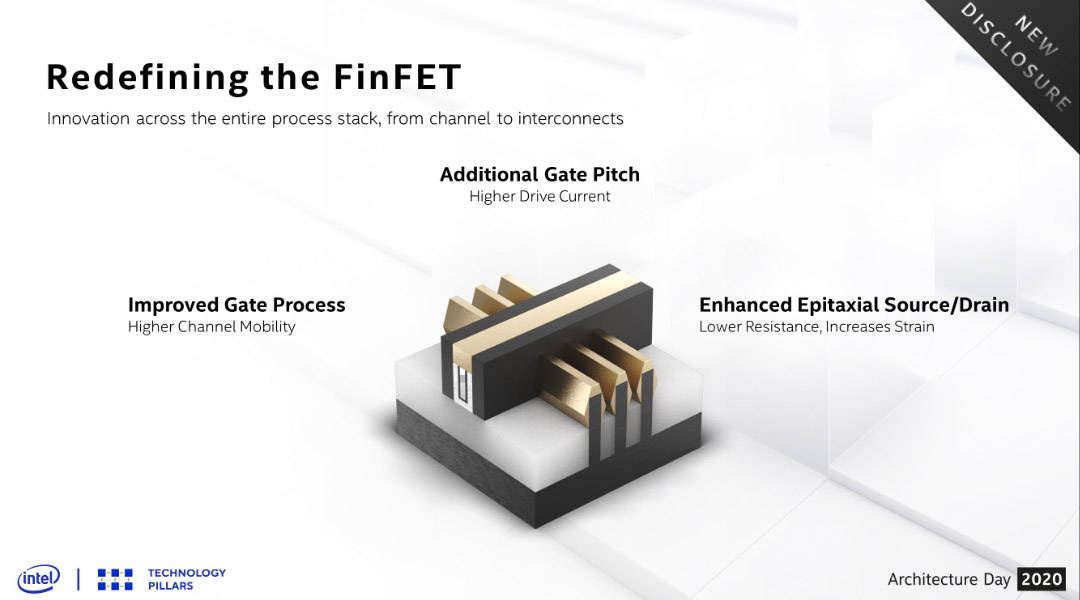

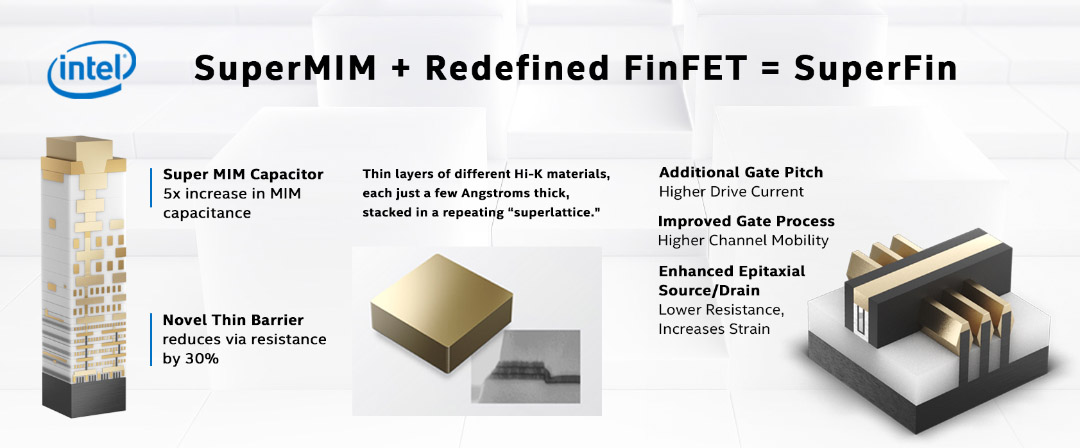

• 經過多年來持續在FinFET電晶體技術方面精益求精的努力,英特爾正重新定義該技術,以實現史上最大的單節點內技術升級,提供等同轉換至全新製程節點技術的效能改進。10奈米 SuperFin技術將Intel增強型FinFET電晶體與Super MIM電容器結合在一起。SuperFin技術於源極/汲極提供增強的磊晶,改進柵極製程和額外的柵極間距,透過以下方式實現更高的效能:

o 提升源極和汲極結構的磊晶生長,從而提升應力並減小電阻,以允許更多電流通過通道

o 改進柵極製程以驅動更高的通道遷移率,使得電荷載子更快速地移動

o 額外的柵極間距選項,可為需要極致效能的特定晶片功能提供更高的驅動電流

o 新型薄阻障層將通孔電阻降低了30%,增強了互連效能

o 與業界標準相比,英特爾的Super MIM電容於相同的佔用面積,提供5倍的容值,從而降低電壓驟降情況,並顯著提高產品效能。該技術由一種新型Hi-K介電材料所實現,該材料堆疊在厚度僅為數埃(10-10公尺)的超薄層中,形成重複的「超晶格」結構。這是一項業界首創的技術,領先於其他製造商的現有製程能力

• 代號為“Tiger Lake”的英特爾次世代筆電處理器將以10奈米 SuperFin技術為基礎。Tiger Lake目前正在生產並出貨給那些預計在年底節慶季節推出 OEM系統的客戶。

封裝

• 混合接合(Hybrid Bonding)測試晶片已於2020年第二季投片。混合接合是一種可取代當今大多數封裝技術中使用的傳統「熱壓」接合的替代技術。這項新技術可實現極為先進的10微米以下凸點間距(含10微米),進而提供更高的互連密度、頻寬和更低的功耗。

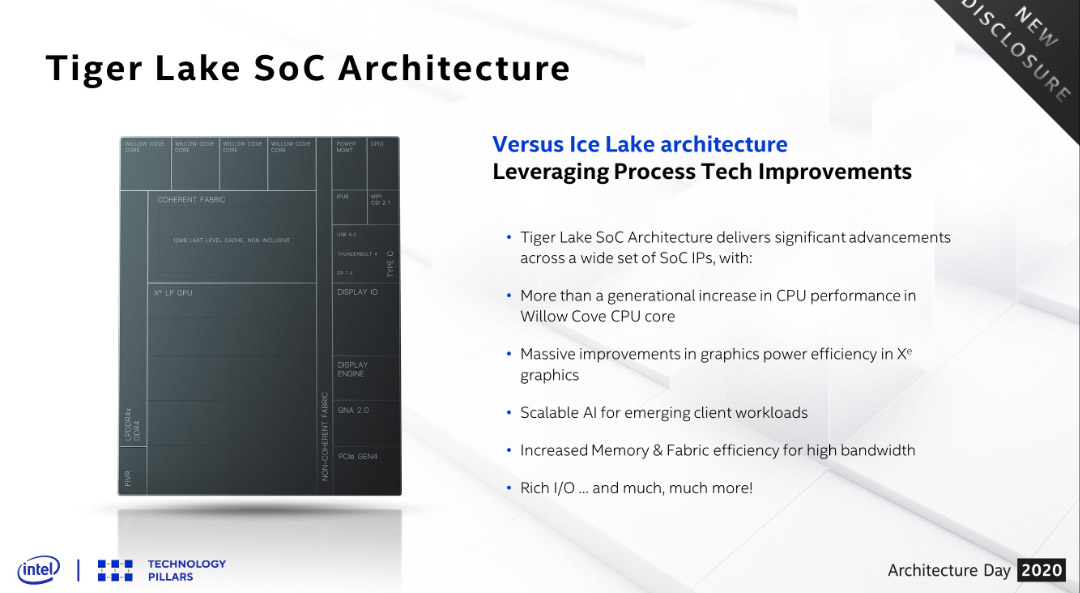

Willow Cove和Tiger Lake CPU架構

• Willow Cove是英特爾的次世代CPU微架構。採用最新的製程,10奈米SuperFin技術,並植基於Sunny Cove微架構之上,Willow Cove帶來了超過一個世代的CPU效能提升幅度,以及大幅度改善時脈表現和提升電力效率。並為更大的non-inclusive 1.25MB L2快取,導入重新設計的快取架構,並透過Intel® 控制流強制技術(Intel® Control-flow Enforcement Technology)增強了安全性。

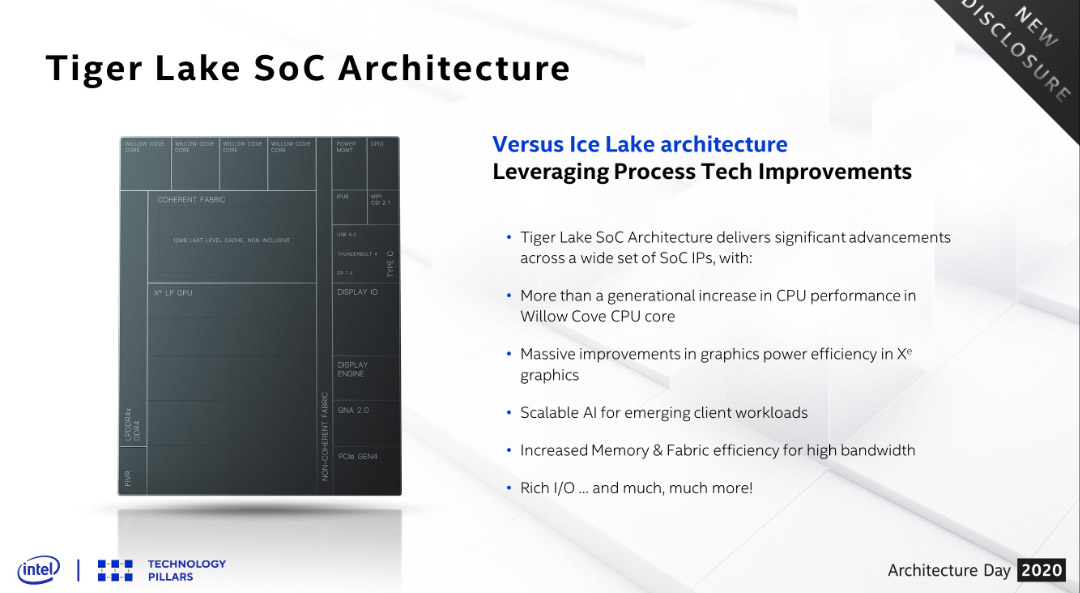

• Tiger Lake將在關鍵向量運算方面提供智慧效能和突破性的進步。透過CPU、AI加速器最佳化,以及首款整合 Xe-LP 繪圖為架構的系統單晶片架構,Tiger Lake將帶來超過一個世代的CPU效能提升幅度、大幅度改善AI效能、繪圖效能的巨大躍升,並在系統單晶片當中享有完整的最佳IP組合,例如新的整合式Thunderbolt 4。Tiger Lake 系統單晶片架構提供:

o 全新Willow Cove CPU核心 – 利用10奈米 SuperFin技術進展顯著提升頻率

o 最多達96個EU(執行單元)的新型Xe繪圖,顯著提升每瓦效率

o 電源管理 – 一致性結構中的自律DVFS,提高FIVR效率

o 架構和記憶體 – 一致性結構頻寬增加2倍,記憶體頻寬約達86GB/s,經過驗證的LP4x-4267、DDR4-3200;LP5-5400架構相容性

o GNA 2.0專用IP,可從CPU卸載並進行低功耗神經網路推論。與單純使用CPU相比,使用GNA的CPU使用率降低約20%(噪音抑制工作負載)

o IO-CPU整合TB4 / USB4、PCIe Gen 4,可替裝置實現低延遲、高頻寬的記憶體存取

o 顯示器 – 於多個高解析度畫面和記憶體之間,提供最高達64GB/s的同步頻寬。與記憶體之間提供專用結構通道,用來確保服務品質

o IPU6 – 可支援多達6個4K30視訊串流、2千7百萬畫素感光元件;最高提供4K90和4千2百萬畫素影像架構相容能力

混合式架構

英特爾透過其次世代客戶端產品Alder Lake推進其混合式架構。Alder Lake將結合英特爾即將推出的Golden Cove和Gracemont兩種架構,並進行最佳化以提供出色的每瓦效能。

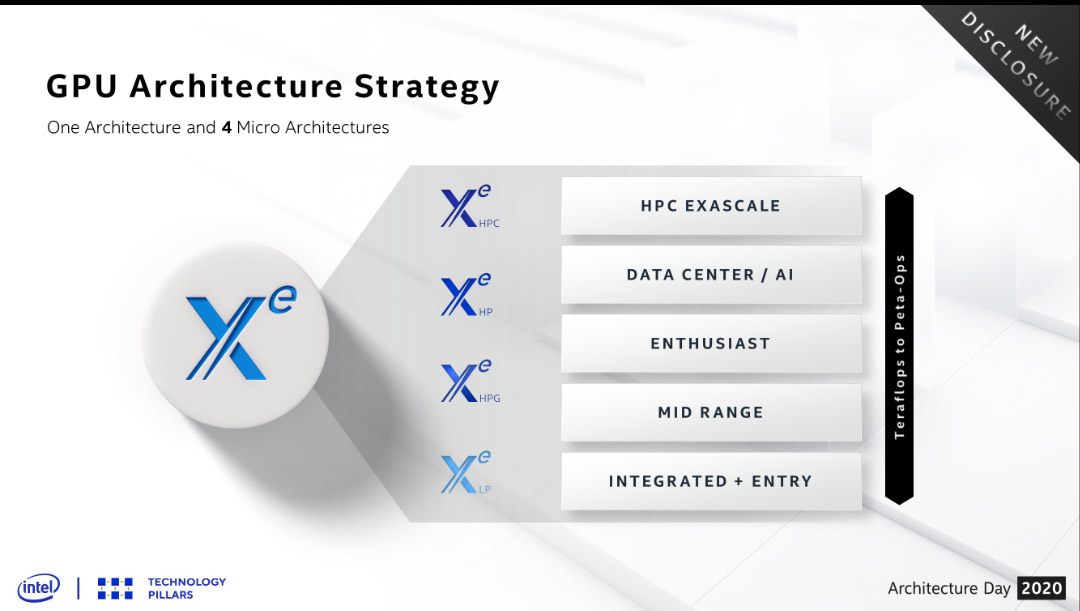

Xe 繪圖架構

• 英特爾詳細介紹了經過最佳化的Xe-LP(低功耗)微架構和軟體,可為行動平台提供高效率的效能。 Xe-LP是英特爾用於PC和行動運算平台的最高效架構,具備多達96個EU,並擁有新的架構設計,包括非同步運算,視圖實體化,取樣器回饋,更新支援AV1的媒體引擎和更新的顯示引擎。透過即時遊戲調整、擷取與串流、影像銳化等技術,帶來新的終端使用者功能。在軟體最佳化方面,Xe-LP將透過新的DX11路徑和最佳化編譯器來改進驅動程式。

• Intel® Server GPU (SG1) 是英特爾針對資料中心,第一款以Xe架構為基礎的獨立GPU。SG1將4個DG1效能以small form factor的規格帶進資料中心,其目標是實現低延遲、高密度Android雲端遊戲和影片串流。SG1將在近期內開始量產,並於今年稍晚出貨。

• 英特爾首款以Xe架構為基礎,代號為DG1的獨立GPU已開始投產,預計在2020年開始出貨。具備前期存取權限的使用者現在可透過Intel® DevCloud取得DG1可用資源。正如年初在CES所披露的資訊,DG1將是英特爾為PC提供的首款,基於Xe-LP微架構的獨立GPU。

• 第一款Xe-HP晶片已於實驗室完成啟動測試。Xe-HP是業界首款多重砌磚式(multi-tiled)、高度可擴展的高效能架構,可提供資料中心機架層級的媒體效能、GPU可擴展性和AI最佳化。如同多核心CPU的概念,運算範圍能夠於1個裸晶區塊,或是2個、4個區塊之間動態調整。在架構日期間,英特爾展示Xe-HP單一區塊對10個完整高畫質4K影片串流進行轉碼,效能可達60FPS,此外還展示了Xe-HP在多個區塊上的運算可擴展性。英特爾正與主要客戶一同測試Xe-HP,並計劃在Intel DevCloud中為開發人員提供Xe-HP資源。Xe-HP將於明年上市。

• 英特爾推出Xe微架構新版本Xe-HPG,這是一款為遊戲最佳化的微架構,結合Xe-LP良好的效能/功耗元素,加上Xe-HP的規模優勢加大組態,並從Xe-HPC最佳化運算頻率。為提升每單位成本的效能,加入基於GDDR6的新記憶體子系統,且Xe-HPG將支援光線追蹤加速功能。Xe-HPG預計於2021年開始出貨。

• Intel® Graphics Command Center (IGCC) 導入即時遊戲調整和遊戲銳化等新功能。

o 即時遊戲調整是針對各款遊戲特別調整的驅動程式,修正和最佳化可以比以前更快地推送給終端使用者,無需下載和安裝完整的驅動程式,使用者僅需針對每個遊戲執行一次選擇加入即可。

o 遊戲銳化為一項新的後處理功能,使用感知調整式銳化功能來銳化遊戲影像 – 這是一種基於運算著色器的適應性銳化演算法,可提高遊戲影像的清晰度。此功能對於使用解析度縮放以平衡效能和影像品質的遊戲特別有用,並且是IGCC當中的可選功能。

資料中心架構

• Ice Lake是英特爾首款基於10奈米製程的Xeon Scalable產品,目標於今年年底開始出貨,Ice Lake伺服器產品面對橫跨多項工作的吞吐量與回應性,均可提供相當出色的效能。它將帶來一系列的新技術,包括全記憶體加密、PCIe Gen 4、8條記憶體通道,以及提升加密運算的指令集強化。用於網路儲存和物聯網的版本,也將導入作為Ice Lake家族的一部分。

• Sapphire Rapids是基於強化版SuperFin技術的英特爾次世代Xeon Scalable處理器,其將提供領先的產業標準技術,包括DDR5、PCIe Gen 5和Compute Express Link 1.1。Sapphire Rapids將成為美國Argonne國家實驗室Aurora Exascale超級電腦系統中使用的CPU。其將使用名為Advanced Matrix Extensions(AMX)的新款加速器,來延續我們內建AI加速的策略。Sapphire Rapids預計將於2021年下半年開始首批生產出貨。

• 英特爾展示了我們在推動FPGA技術上的持續創新和連續第三代收發器的領先地位,英特爾現在擁有全球首款次世代224G-PAM4 發送收發器。

軟體

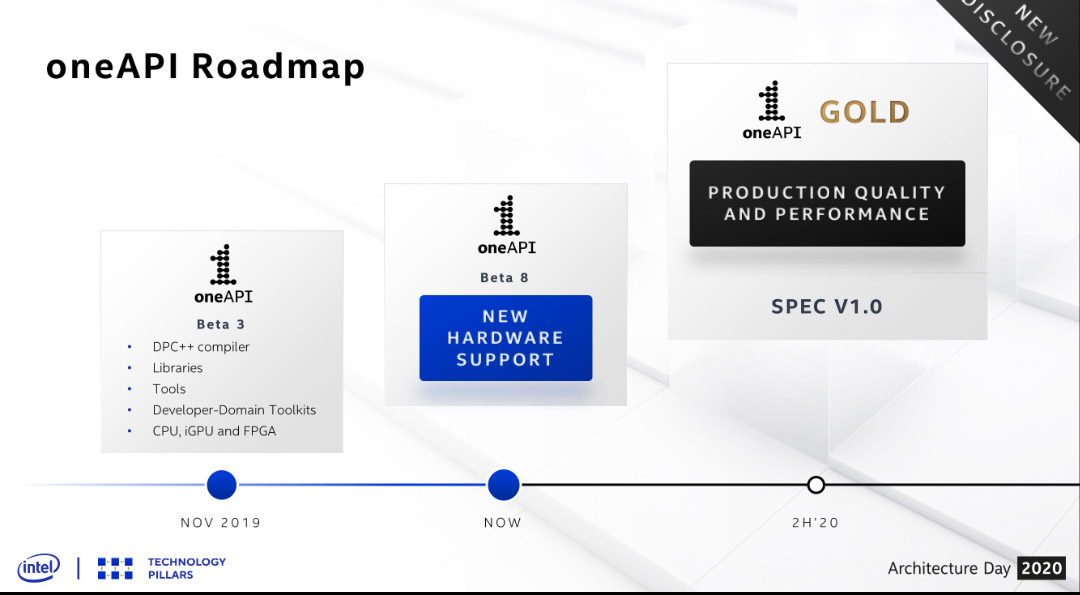

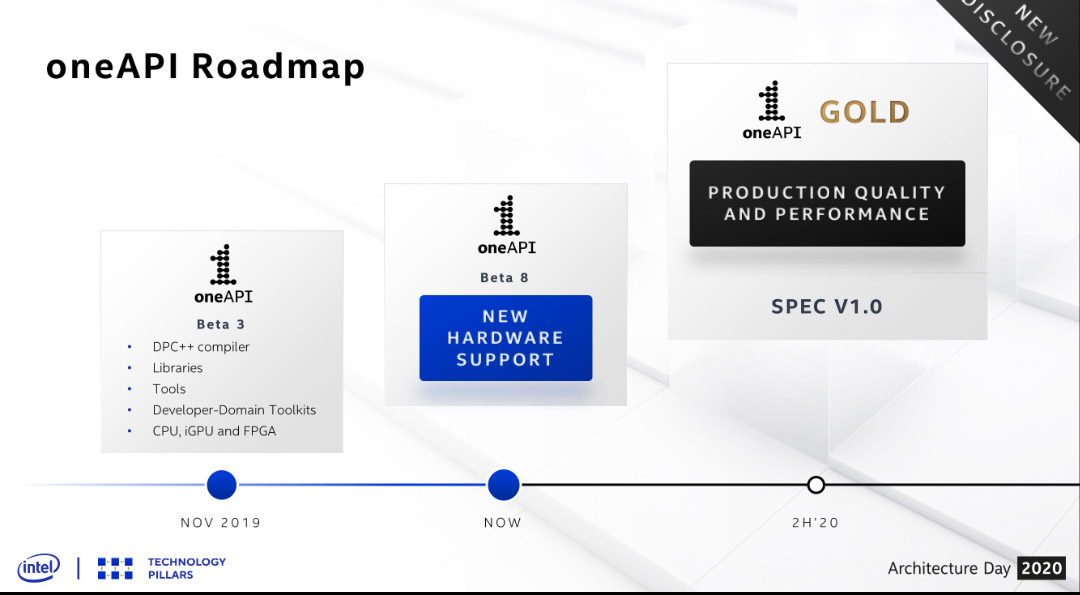

oneAPI Gold版本將於今年稍晚推出,為開發人員提供一款在純量、向量、矩陣和空間體系結構上具有量產品質和效能的解決方案。 英特爾於7月發布了第八版的oneAPI Beta,為分佈式資料分析、渲染效能、效能分析以及英特爾影片與執行緒資料庫提供了新功能和升級強化。DG1獨立GPU目前可供Intel® DevCloud中的前期存取開發人員使用,提供對資料庫和工具組的存取,使他們能夠在拿到硬體之前就開始使用oneAPI編寫軟體。

以上新聞訊息代表著英特爾科技六大創新支柱的進展。英特爾正在充分利用我們獨特的優勢,提供在CPU、GPU、加速器和FPGA中部署的純量、向量、矩陣和空間架構組合,透過開放的產業標準程式設計模型oneAPI進行統整,以簡化應用程式的開發過程。

2020年8月13日 – 英特爾首席架構師 Raja Koduri、英特爾院士及其架構師團隊,詳細介紹了英特爾在科技六大創新支柱上所取得的進展。英特爾揭示其10奈米SuperFin技術,代表了公司歷史上最大的單一節點內升級功能,提供等同於轉換至全新製程節點技術的效能改進。

英特爾公司還公佈Willow Cove微架構和針對行動客戶端的Tiger Lake 系統單晶片架構的詳細資訊,並首度揭示了其完全可擴展的Xe繪圖架構,這些架構可滿足從消費端至高效能運算,再到遊戲用途的各個市場。英特爾將其解藕晶片設計方式、結合先進的封裝技術,XPU產品和以軟體為中心的策略,致力為客戶提供領先效能的全方位解決方案。

10奈米 SuperFin 技術

• 經過多年來持續在FinFET電晶體技術方面精益求精的努力,英特爾正重新定義該技術,以實現史上最大的單節點內技術升級,提供等同轉換至全新製程節點技術的效能改進。10奈米 SuperFin技術將Intel增強型FinFET電晶體與Super MIM電容器結合在一起。SuperFin技術於源極/汲極提供增強的磊晶,改進柵極製程和額外的柵極間距,透過以下方式實現更高的效能:

o 提升源極和汲極結構的磊晶生長,從而提升應力並減小電阻,以允許更多電流通過通道

o 改進柵極製程以驅動更高的通道遷移率,使得電荷載子更快速地移動

o 額外的柵極間距選項,可為需要極致效能的特定晶片功能提供更高的驅動電流

o 新型薄阻障層將通孔電阻降低了30%,增強了互連效能

o 與業界標準相比,英特爾的Super MIM電容於相同的佔用面積,提供5倍的容值,從而降低電壓驟降情況,並顯著提高產品效能。該技術由一種新型Hi-K介電材料所實現,該材料堆疊在厚度僅為數埃(10-10公尺)的超薄層中,形成重複的「超晶格」結構。這是一項業界首創的技術,領先於其他製造商的現有製程能力

• 代號為“Tiger Lake”的英特爾次世代筆電處理器將以10奈米 SuperFin技術為基礎。Tiger Lake目前正在生產並出貨給那些預計在年底節慶季節推出 OEM系統的客戶。

封裝

• 混合接合(Hybrid Bonding)測試晶片已於2020年第二季投片。混合接合是一種可取代當今大多數封裝技術中使用的傳統「熱壓」接合的替代技術。這項新技術可實現極為先進的10微米以下凸點間距(含10微米),進而提供更高的互連密度、頻寬和更低的功耗。

Willow Cove和Tiger Lake CPU架構

• Willow Cove是英特爾的次世代CPU微架構。採用最新的製程,10奈米SuperFin技術,並植基於Sunny Cove微架構之上,Willow Cove帶來了超過一個世代的CPU效能提升幅度,以及大幅度改善時脈表現和提升電力效率。並為更大的non-inclusive 1.25MB L2快取,導入重新設計的快取架構,並透過Intel® 控制流強制技術(Intel® Control-flow Enforcement Technology)增強了安全性。

• Tiger Lake將在關鍵向量運算方面提供智慧效能和突破性的進步。透過CPU、AI加速器最佳化,以及首款整合 Xe-LP 繪圖為架構的系統單晶片架構,Tiger Lake將帶來超過一個世代的CPU效能提升幅度、大幅度改善AI效能、繪圖效能的巨大躍升,並在系統單晶片當中享有完整的最佳IP組合,例如新的整合式Thunderbolt 4。Tiger Lake 系統單晶片架構提供:

o 全新Willow Cove CPU核心 – 利用10奈米 SuperFin技術進展顯著提升頻率

o 最多達96個EU(執行單元)的新型Xe繪圖,顯著提升每瓦效率

o 電源管理 – 一致性結構中的自律DVFS,提高FIVR效率

o 架構和記憶體 – 一致性結構頻寬增加2倍,記憶體頻寬約達86GB/s,經過驗證的LP4x-4267、DDR4-3200;LP5-5400架構相容性

o GNA 2.0專用IP,可從CPU卸載並進行低功耗神經網路推論。與單純使用CPU相比,使用GNA的CPU使用率降低約20%(噪音抑制工作負載)

o IO-CPU整合TB4 / USB4、PCIe Gen 4,可替裝置實現低延遲、高頻寬的記憶體存取

o 顯示器 – 於多個高解析度畫面和記憶體之間,提供最高達64GB/s的同步頻寬。與記憶體之間提供專用結構通道,用來確保服務品質

o IPU6 – 可支援多達6個4K30視訊串流、2千7百萬畫素感光元件;最高提供4K90和4千2百萬畫素影像架構相容能力

混合式架構

英特爾透過其次世代客戶端產品Alder Lake推進其混合式架構。Alder Lake將結合英特爾即將推出的Golden Cove和Gracemont兩種架構,並進行最佳化以提供出色的每瓦效能。

Xe 繪圖架構

• 英特爾詳細介紹了經過最佳化的Xe-LP(低功耗)微架構和軟體,可為行動平台提供高效率的效能。 Xe-LP是英特爾用於PC和行動運算平台的最高效架構,具備多達96個EU,並擁有新的架構設計,包括非同步運算,視圖實體化,取樣器回饋,更新支援AV1的媒體引擎和更新的顯示引擎。透過即時遊戲調整、擷取與串流、影像銳化等技術,帶來新的終端使用者功能。在軟體最佳化方面,Xe-LP將透過新的DX11路徑和最佳化編譯器來改進驅動程式。

• Intel® Server GPU (SG1) 是英特爾針對資料中心,第一款以Xe架構為基礎的獨立GPU。SG1將4個DG1效能以small form factor的規格帶進資料中心,其目標是實現低延遲、高密度Android雲端遊戲和影片串流。SG1將在近期內開始量產,並於今年稍晚出貨。

• 英特爾首款以Xe架構為基礎,代號為DG1的獨立GPU已開始投產,預計在2020年開始出貨。具備前期存取權限的使用者現在可透過Intel® DevCloud取得DG1可用資源。正如年初在CES所披露的資訊,DG1將是英特爾為PC提供的首款,基於Xe-LP微架構的獨立GPU。

• 第一款Xe-HP晶片已於實驗室完成啟動測試。Xe-HP是業界首款多重砌磚式(multi-tiled)、高度可擴展的高效能架構,可提供資料中心機架層級的媒體效能、GPU可擴展性和AI最佳化。如同多核心CPU的概念,運算範圍能夠於1個裸晶區塊,或是2個、4個區塊之間動態調整。在架構日期間,英特爾展示Xe-HP單一區塊對10個完整高畫質4K影片串流進行轉碼,效能可達60FPS,此外還展示了Xe-HP在多個區塊上的運算可擴展性。英特爾正與主要客戶一同測試Xe-HP,並計劃在Intel DevCloud中為開發人員提供Xe-HP資源。Xe-HP將於明年上市。

• 英特爾推出Xe微架構新版本Xe-HPG,這是一款為遊戲最佳化的微架構,結合Xe-LP良好的效能/功耗元素,加上Xe-HP的規模優勢加大組態,並從Xe-HPC最佳化運算頻率。為提升每單位成本的效能,加入基於GDDR6的新記憶體子系統,且Xe-HPG將支援光線追蹤加速功能。Xe-HPG預計於2021年開始出貨。

• Intel® Graphics Command Center (IGCC) 導入即時遊戲調整和遊戲銳化等新功能。

o 即時遊戲調整是針對各款遊戲特別調整的驅動程式,修正和最佳化可以比以前更快地推送給終端使用者,無需下載和安裝完整的驅動程式,使用者僅需針對每個遊戲執行一次選擇加入即可。

o 遊戲銳化為一項新的後處理功能,使用感知調整式銳化功能來銳化遊戲影像 – 這是一種基於運算著色器的適應性銳化演算法,可提高遊戲影像的清晰度。此功能對於使用解析度縮放以平衡效能和影像品質的遊戲特別有用,並且是IGCC當中的可選功能。

資料中心架構

• Ice Lake是英特爾首款基於10奈米製程的Xeon Scalable產品,目標於今年年底開始出貨,Ice Lake伺服器產品面對橫跨多項工作的吞吐量與回應性,均可提供相當出色的效能。它將帶來一系列的新技術,包括全記憶體加密、PCIe Gen 4、8條記憶體通道,以及提升加密運算的指令集強化。用於網路儲存和物聯網的版本,也將導入作為Ice Lake家族的一部分。

• Sapphire Rapids是基於強化版SuperFin技術的英特爾次世代Xeon Scalable處理器,其將提供領先的產業標準技術,包括DDR5、PCIe Gen 5和Compute Express Link 1.1。Sapphire Rapids將成為美國Argonne國家實驗室Aurora Exascale超級電腦系統中使用的CPU。其將使用名為Advanced Matrix Extensions(AMX)的新款加速器,來延續我們內建AI加速的策略。Sapphire Rapids預計將於2021年下半年開始首批生產出貨。

• 英特爾展示了我們在推動FPGA技術上的持續創新和連續第三代收發器的領先地位,英特爾現在擁有全球首款次世代224G-PAM4 發送收發器。

軟體

oneAPI Gold版本將於今年稍晚推出,為開發人員提供一款在純量、向量、矩陣和空間體系結構上具有量產品質和效能的解決方案。 英特爾於7月發布了第八版的oneAPI Beta,為分佈式資料分析、渲染效能、效能分析以及英特爾影片與執行緒資料庫提供了新功能和升級強化。DG1獨立GPU目前可供Intel® DevCloud中的前期存取開發人員使用,提供對資料庫和工具組的存取,使他們能夠在拿到硬體之前就開始使用oneAPI編寫軟體。

以上新聞訊息代表著英特爾科技六大創新支柱的進展。英特爾正在充分利用我們獨特的優勢,提供在CPU、GPU、加速器和FPGA中部署的純量、向量、矩陣和空間架構組合,透過開放的產業標準程式設計模型oneAPI進行統整,以簡化應用程式的開發過程。