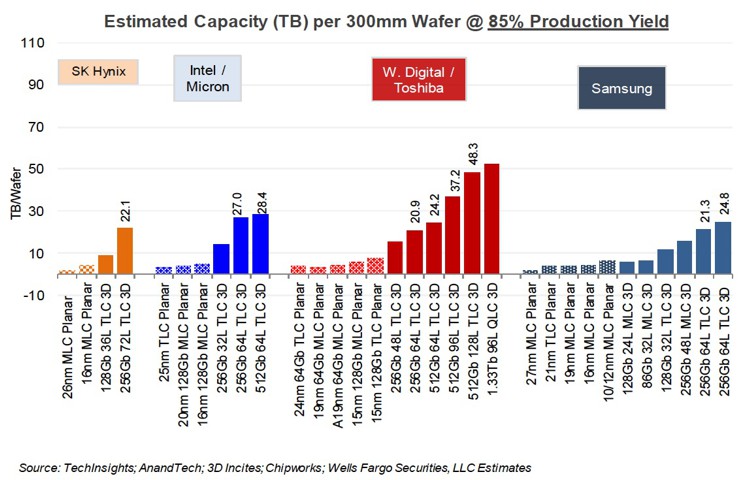

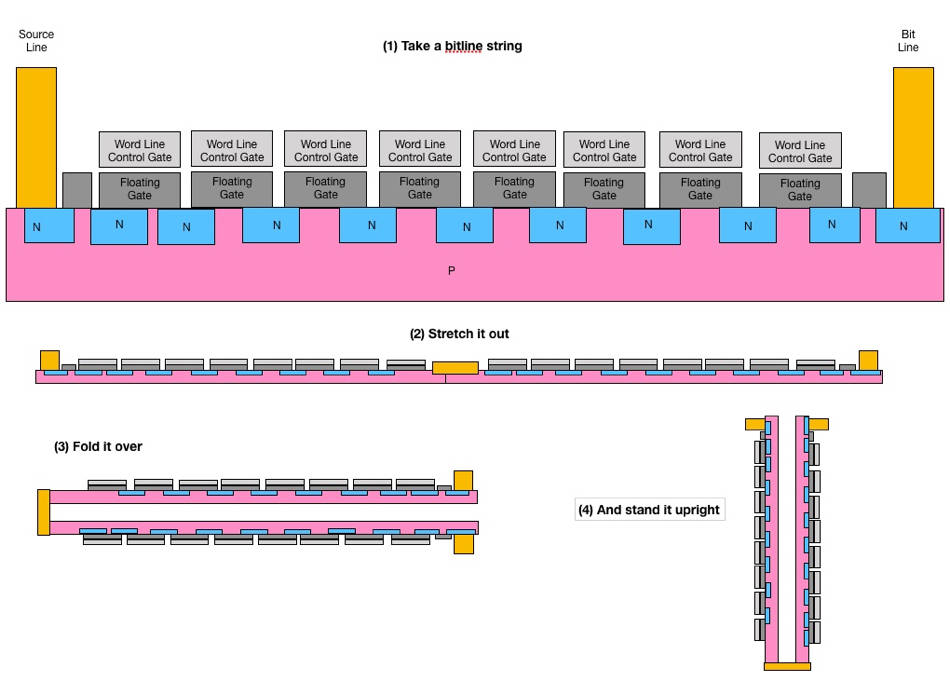

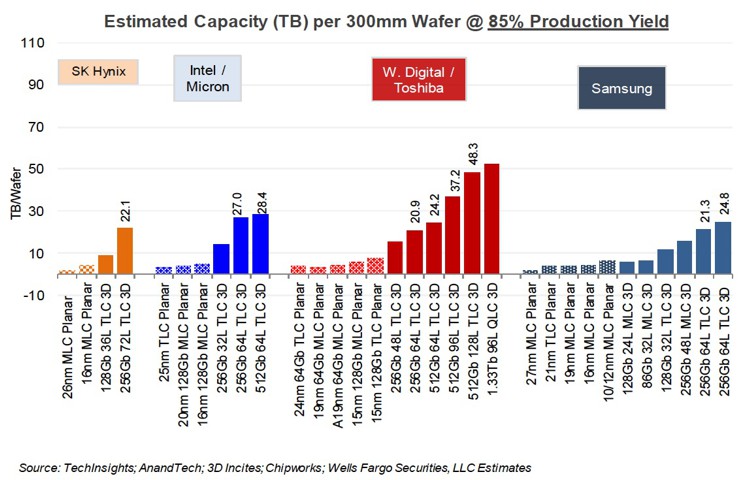

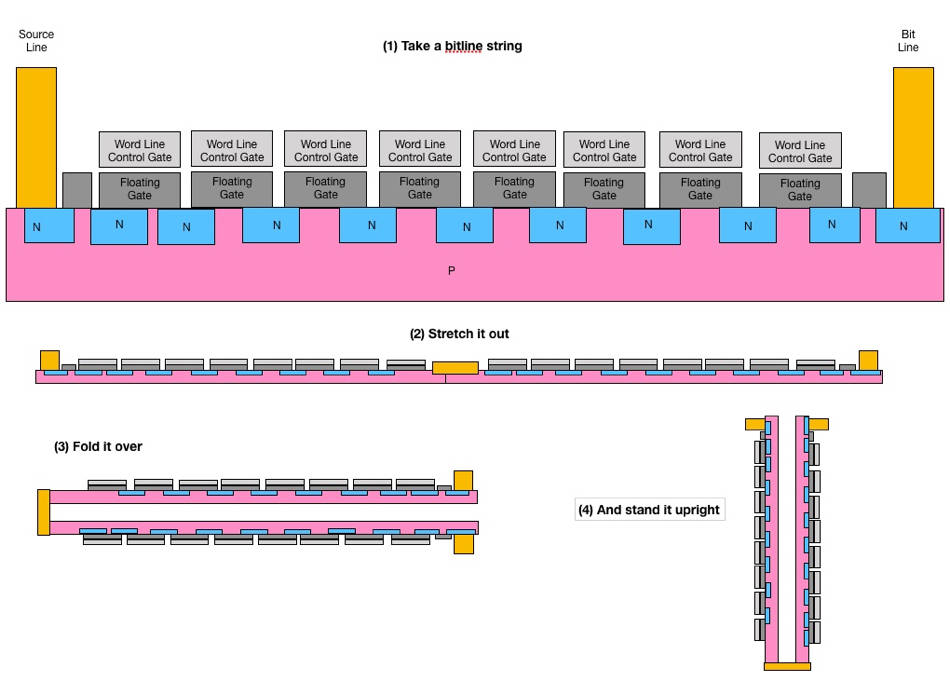

最近 Toshiba 與 WD 的128層堆疊 3D NAND 的部分資料曝光,它將會被命名為 BiCS 5,而96層堆疊的 3D NAND 則名為 BiCS 4,128層堆疊快閃記憶體將會使用 CuA 設計,邏輯電路層在晶片的底部,而數據層則堆疊在上方,與非 CuA 技術相比這可把晶片尺寸縮小15%。目前公佈出來的128層堆疊 3D NAND 使用 TLC 設計,儲存密度接近96層堆疊的 3D QLC,儲存密度比自家的96層堆疊 3D TLC 提升了29.8%,如果採用 QLC 設計的話儲存密度相對更高。

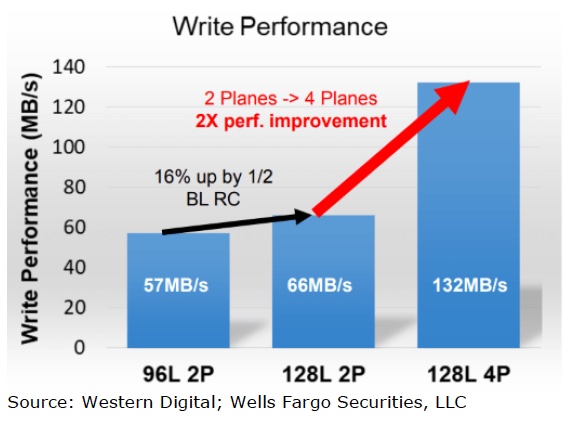

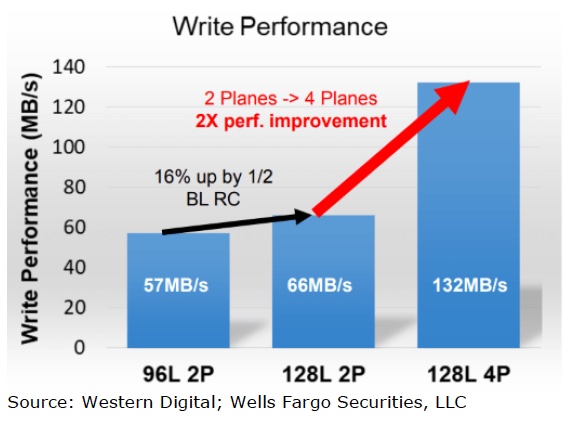

BiCS 5 的快閃記憶體單 die 採用 4 Planes 設計,而與 2 Planes 設計相比寫入速度從66MB/s提升到132MB/s,這意味著 SSD 在 SLC Cache 用光之後 TLC 的原始寫入速度會變得不會那麼難看,不過具體的寫入速度表現還得看主控的算法,如果用全盤 SLC Cache 的方案,Cache 用光後效能依然難看。

預計 Toshiba 與 WD 會在2020年末開始投產128層堆疊的 BiCS-5,而產能應該在2021年才會提上去,屆時才能看到對應的 SSD 產品。

來源:

https://blocksandfiles.com/2019/03/04/wd-toshiba-add-32-layers-to-reach-128-layer-3d-nand/

https://www.expreview.com/67125.html

BiCS 5 的快閃記憶體單 die 採用 4 Planes 設計,而與 2 Planes 設計相比寫入速度從66MB/s提升到132MB/s,這意味著 SSD 在 SLC Cache 用光之後 TLC 的原始寫入速度會變得不會那麼難看,不過具體的寫入速度表現還得看主控的算法,如果用全盤 SLC Cache 的方案,Cache 用光後效能依然難看。

預計 Toshiba 與 WD 會在2020年末開始投產128層堆疊的 BiCS-5,而產能應該在2021年才會提上去,屆時才能看到對應的 SSD 產品。

來源:

https://blocksandfiles.com/2019/03/04/wd-toshiba-add-32-layers-to-reach-128-layer-3d-nand/

https://www.expreview.com/67125.html

最後編輯: