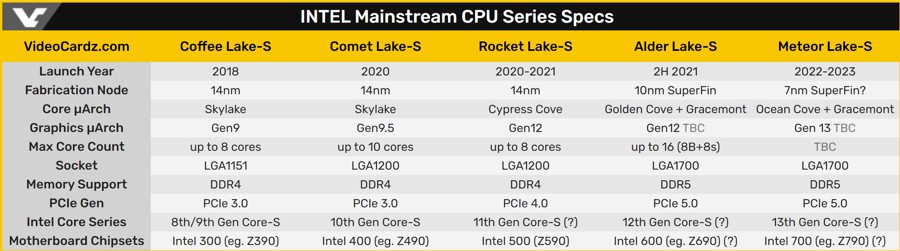

Intel 預計在明年推出第12代桌面版處理器,代號為 Alder Lake-S,採用大小核心混合架構,大核心 Golden Cove 加上小核心 Gracemont。

這並不是 x86 處理器首次用上混合技術,Intel 今年稍早就已推出用於超低功耗的第11代 Lakefield,該系列採用單個大 Sunny Cove 加上4個 Tremont 小核心。

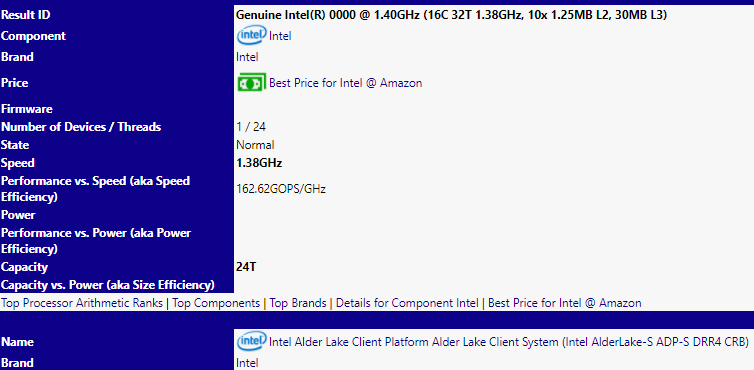

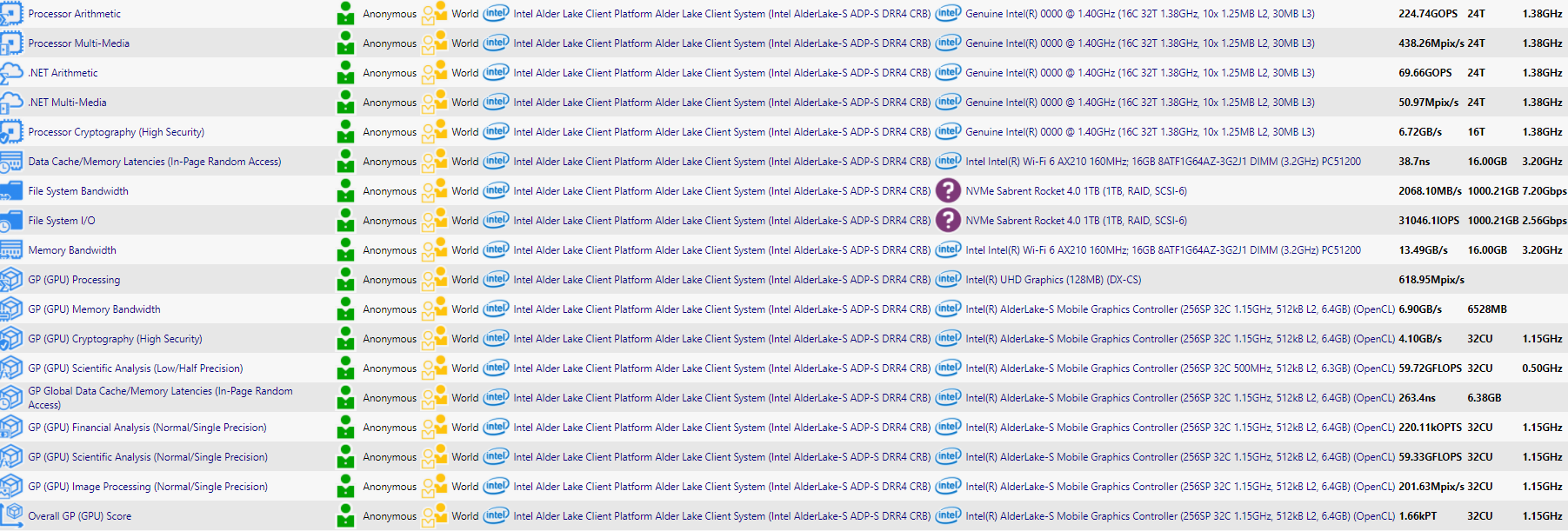

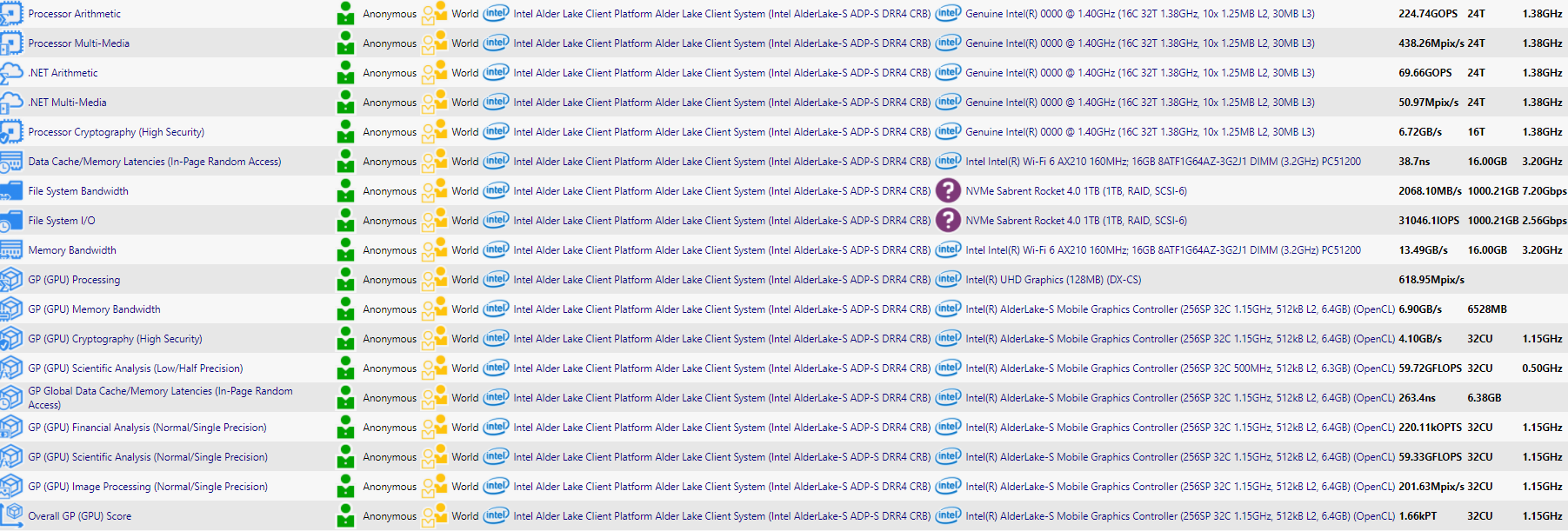

Intel 第12代的 Alder Lake-S 最多將會採用8大核心+8小核心配置,最近一些基準測試已經出現在 Sisoftware 資料庫上。從截圖上可以看到該設備具有16個物理核心和32個執行緒,從而確認了 Alder Lake-S 的最大核心數。

該 CPU 具有 10x1.25MB 的 L2 快取和 30MB 的 L3 快取。Golden Cove 的 L2 和 L3 快取大小似乎與 Willow Cove 相同,而較小的 Gracemont 核心似乎是共用快取。“ DRR4”可能是誤植,可能是指 DDR4,先前 Alder Lake-S 傳言將支援 DDR5 以及 DDR4 記憶體,DDR4 可能用於移動版本,DDR5 是桌面版。

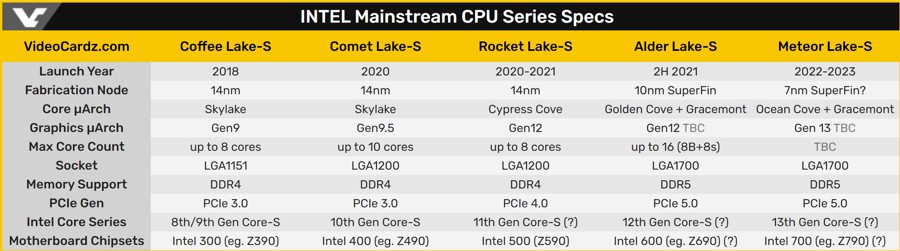

來源提到了Alder Lake-S 將有 PCIe 5.0 的支援,先前 Intel 所曝光的文檔中確實有看到 Gen5,不過是不是指 PCIe 5.0 還有待確認,有消息稱這是 Gen5 VR 測試設備,不代表 PCIe Gen5。

來源

這並不是 x86 處理器首次用上混合技術,Intel 今年稍早就已推出用於超低功耗的第11代 Lakefield,該系列採用單個大 Sunny Cove 加上4個 Tremont 小核心。

Intel 第12代的 Alder Lake-S 最多將會採用8大核心+8小核心配置,最近一些基準測試已經出現在 Sisoftware 資料庫上。從截圖上可以看到該設備具有16個物理核心和32個執行緒,從而確認了 Alder Lake-S 的最大核心數。

該 CPU 具有 10x1.25MB 的 L2 快取和 30MB 的 L3 快取。Golden Cove 的 L2 和 L3 快取大小似乎與 Willow Cove 相同,而較小的 Gracemont 核心似乎是共用快取。“ DRR4”可能是誤植,可能是指 DDR4,先前 Alder Lake-S 傳言將支援 DDR5 以及 DDR4 記憶體,DDR4 可能用於移動版本,DDR5 是桌面版。

來源提到了Alder Lake-S 將有 PCIe 5.0 的支援,先前 Intel 所曝光的文檔中確實有看到 Gen5,不過是不是指 PCIe 5.0 還有待確認,有消息稱這是 Gen5 VR 測試設備,不代表 PCIe Gen5。

來源