Intel前幾天慶祝了半導體業界黃金法則——摩爾定律,通過更先進的製程不斷提升晶體管密度是Intel制勝的關鍵,他們也以此維護了摩爾定律的準確。如今Intel的製造製程已經是14nm,下一步就是10nm製程,面臨的挑戰還會更多,Intel實際上也延期了10nm製程進程,但Intel手中的黑科技可不少,分析認為Intel將在10nm製程節點啟用量子阱晶體管(Quantum Well FET,簡稱QWFET),還會使用銦鎵砷及應變鍺兩種新型半導體材料。

如今的集成電路基本上都是基於矽基材料,晶體管的性能、運行電壓及電流都與晶體管的結構有關,因此整體功耗密度相同的情況下,晶體管的功耗與電壓的平方成正比——當然,晶體管密度是在不斷提升到的(這是摩爾定律的內容)。這個規律是1975年IBM公司的研究人員Robert Dennard總結的,因此這個定律也以他的名字命名——這就是Dennard scaling定律的來源。

這個定律在2000年代前都是適用的,但2005年David Wang在IEDM會議上提出,晶體管的性能不能再通過幾何結構而提升,功耗問題越來越嚴重,而功耗來源於兩個方面——漏電流帶來的靜態功耗以及晶體管開關帶來的動態功耗(注:動態功耗有個公式Switching power = C*V2*F)。

現在的情況就是晶體管越小,漏電流越來越嚴重,解決功耗問題的重點就轉移到漏電流這方面來了,Intel曾經在90nm製程使用應變矽製程,45nm節點使用HKMG(高K金屬柵極)製程,22nm製程使用FinFET晶體管製程,這都有助於降低漏電流,進而降低功耗。

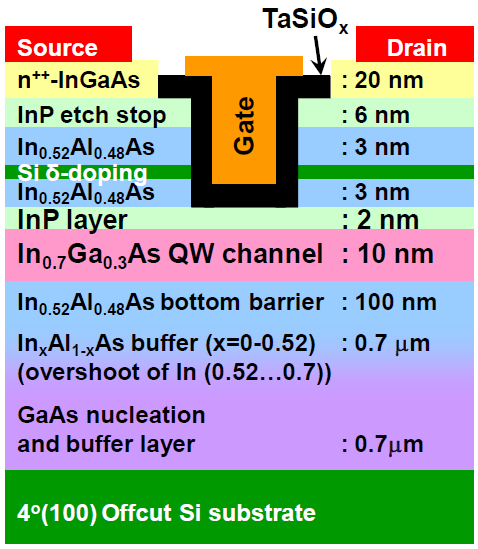

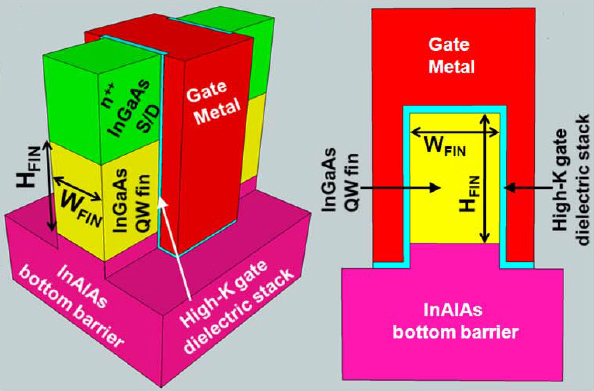

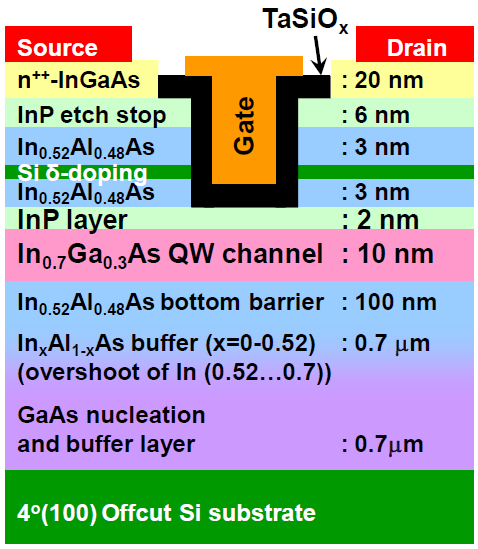

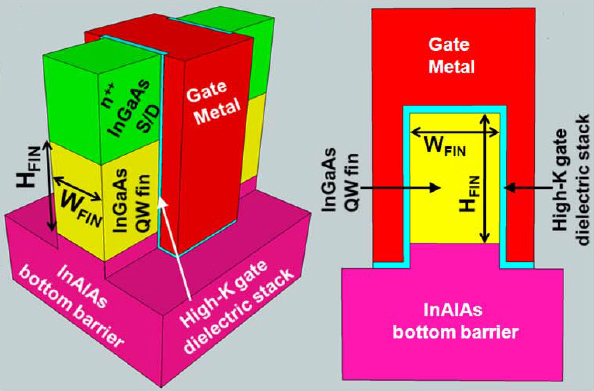

銦鎵砷晶體管結構

似乎還沒回到正題上,不過背景內容我們不說這麼多了,RealWorldTech網站日前刊發了一篇文章分析Intel公司的10nm製程,分析師David Kanter認為Intel有很大可能會在10nm製程啟用QWFEN量子阱晶體管製程,同時還會使用新型的半導體材料,N型使用銦鎵砷(In0.53Ga0.47As),P型使用應變鍺(strained germanium)

按照他的分析,Intel最早會在2016年的10nm製程上使用這些黑科技,將晶體管運行電壓從0.7V降低到0.5V,而三星、TSMC、Globalfoundries等公司要等到7nm製程才有可能使用這些新技術,依然要比Intel落後一代。

來源:http://www.expreview.com/40115.html

如今的集成電路基本上都是基於矽基材料,晶體管的性能、運行電壓及電流都與晶體管的結構有關,因此整體功耗密度相同的情況下,晶體管的功耗與電壓的平方成正比——當然,晶體管密度是在不斷提升到的(這是摩爾定律的內容)。這個規律是1975年IBM公司的研究人員Robert Dennard總結的,因此這個定律也以他的名字命名——這就是Dennard scaling定律的來源。

這個定律在2000年代前都是適用的,但2005年David Wang在IEDM會議上提出,晶體管的性能不能再通過幾何結構而提升,功耗問題越來越嚴重,而功耗來源於兩個方面——漏電流帶來的靜態功耗以及晶體管開關帶來的動態功耗(注:動態功耗有個公式Switching power = C*V2*F)。

現在的情況就是晶體管越小,漏電流越來越嚴重,解決功耗問題的重點就轉移到漏電流這方面來了,Intel曾經在90nm製程使用應變矽製程,45nm節點使用HKMG(高K金屬柵極)製程,22nm製程使用FinFET晶體管製程,這都有助於降低漏電流,進而降低功耗。

銦鎵砷晶體管結構

似乎還沒回到正題上,不過背景內容我們不說這麼多了,RealWorldTech網站日前刊發了一篇文章分析Intel公司的10nm製程,分析師David Kanter認為Intel有很大可能會在10nm製程啟用QWFEN量子阱晶體管製程,同時還會使用新型的半導體材料,N型使用銦鎵砷(In0.53Ga0.47As),P型使用應變鍺(strained germanium)

按照他的分析,Intel最早會在2016年的10nm製程上使用這些黑科技,將晶體管運行電壓從0.7V降低到0.5V,而三星、TSMC、Globalfoundries等公司要等到7nm製程才有可能使用這些新技術,依然要比Intel落後一代。

來源:http://www.expreview.com/40115.html