AMD 雖然發布了7nm製程的 Zen 2 架構,但相關訊息並不多,首發是以伺服器為主的 EPYC,代號 Rome,目前所知 Zen 2 在架構在前端、浮點、快取等方面都做了改善,也加倍了浮點頻寬到256bit、核心密度,並降低了一半的操作功耗,且增加了 PCI-E 4.0 的支援。

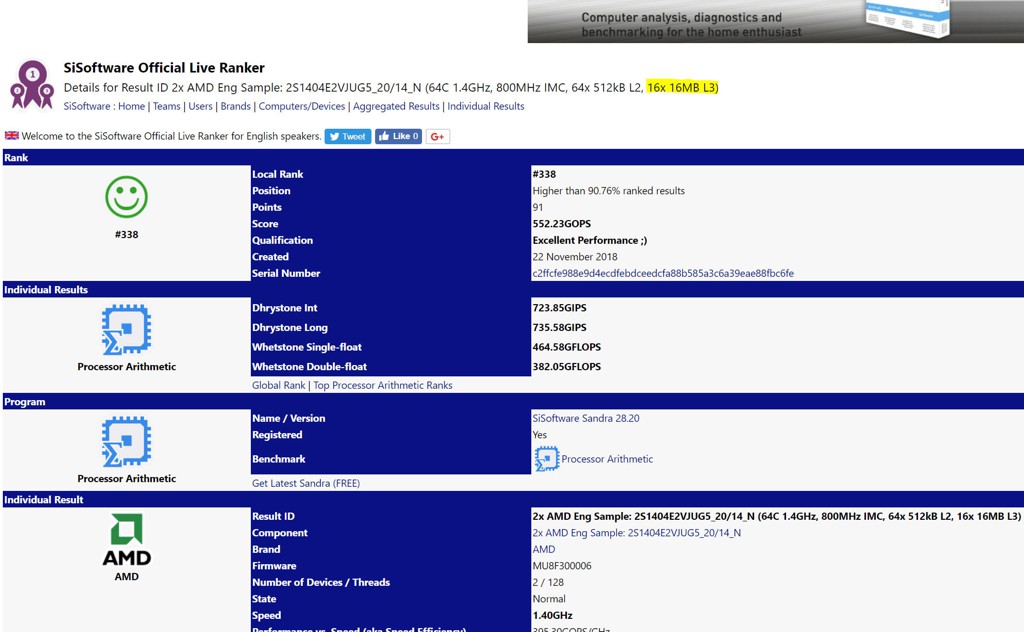

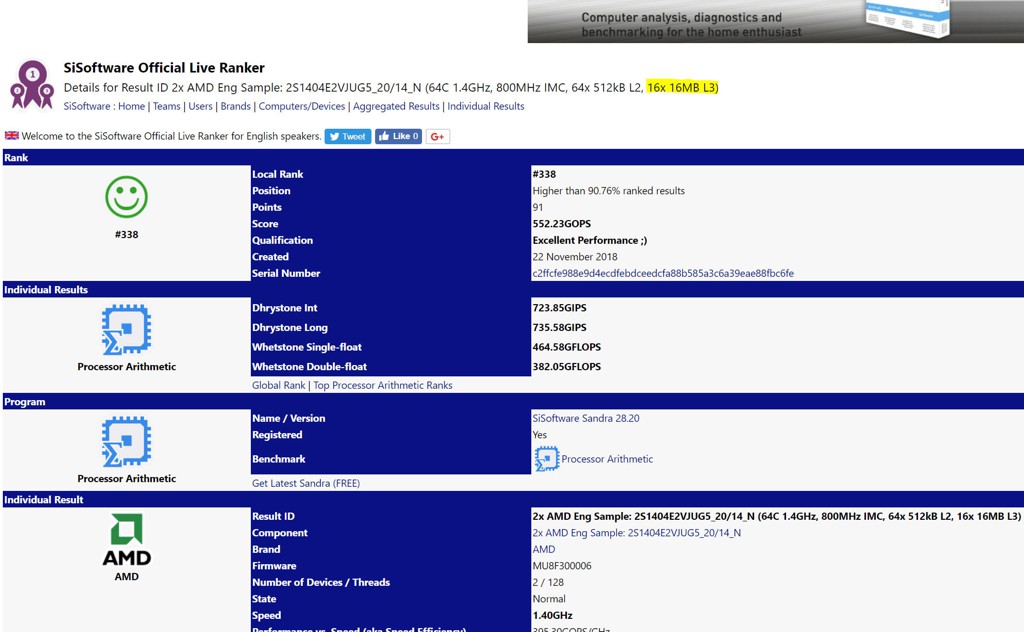

最近 SiSoft SANDRA 的資料庫上有更多消息曝光,截圖上得知這是一個雙路 Rome 架構 EPYC 處理器的系統,CPU 還處於 ES 階段,時脈是1.4GHz,L2 快取大小是每核心512KB,這和現在的 Zen 架構是一樣的,但 L3 快取變成了每 CCX 16MB,說明了 Zen2 架構的 L3 快取比現在翻了一倍,而整個64核的 EPYC 處理器擁有256MB的 L3,這 L3 的容量是相當驚人的,可能是由於 Rome 架構的8通道記憶體控制器和 PCI-E 控制器是在另外的I/O晶片上,需要更大的 L3 快取來降低通訊延遲。

來源:

https://www.techpowerup.com/249952/amd-doubles-l3-cache-per-ccx-with-zen-2-rome

http://www.expreview.com/65470.html

最近 SiSoft SANDRA 的資料庫上有更多消息曝光,截圖上得知這是一個雙路 Rome 架構 EPYC 處理器的系統,CPU 還處於 ES 階段,時脈是1.4GHz,L2 快取大小是每核心512KB,這和現在的 Zen 架構是一樣的,但 L3 快取變成了每 CCX 16MB,說明了 Zen2 架構的 L3 快取比現在翻了一倍,而整個64核的 EPYC 處理器擁有256MB的 L3,這 L3 的容量是相當驚人的,可能是由於 Rome 架構的8通道記憶體控制器和 PCI-E 控制器是在另外的I/O晶片上,需要更大的 L3 快取來降低通訊延遲。

來源:

https://www.techpowerup.com/249952/amd-doubles-l3-cache-per-ccx-with-zen-2-rome

http://www.expreview.com/65470.html