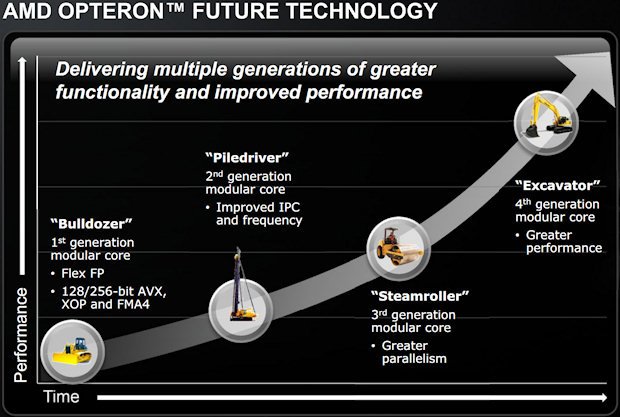

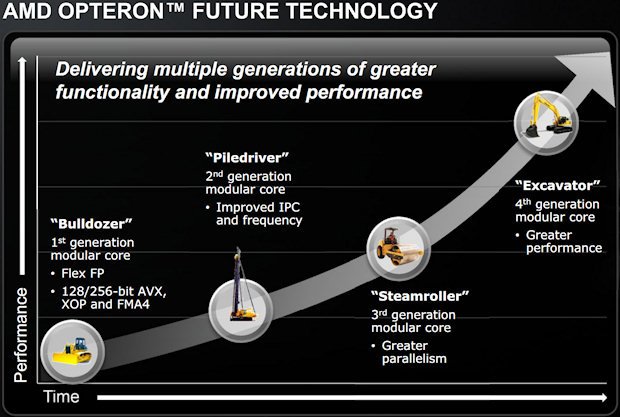

按照AMD的規劃,“Bulldozer”推土機是第一代模塊化CPU,第二代則是Piledriver打樁機,將於今年下半年發布,而且使用了Cyclos半導體的Resonant Clock Mesh技術以提高性能。 到了2013年就該“Steamroller”壓路機出場了,AMD對它的描述是“Greater parallelism”,強調並行性能提升。

有關壓路機的架構設計目前還是捕風捉影的階段,日前AMD研究部門的David M. Russinoff發布的一篇論文中證實了Steamroller將會採用radix-8 SRT浮點模塊,每週期運行指令將從目前的radix- 4單元的2條提高到3條。

Steamroller改變的是CPU中除法器(Divider)單元的設計, 有興趣的可以參考wiki的解釋 。 David M. Russinoff參與了Llano APU的設計,其DIV單元與前代K10沒有DIV硬件支持的設計有所不同,推土機繼承了K10的設計,FMAC(浮點累積乘單元)中的除法器功能有限。 現在Steamroller的設計類似Llano,當然不會是100%相同,因為它使用的是radix-8而非Llano的radix-4,每週期執行的指令數從2條提高到了3條。

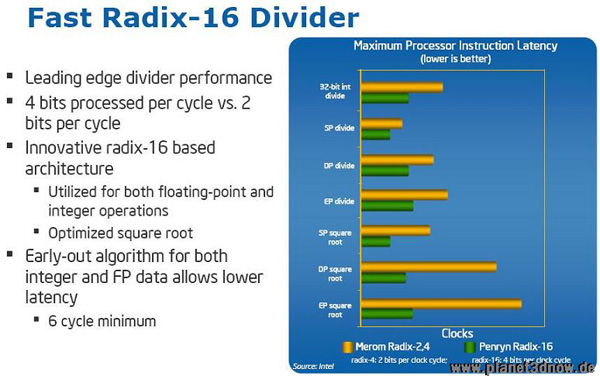

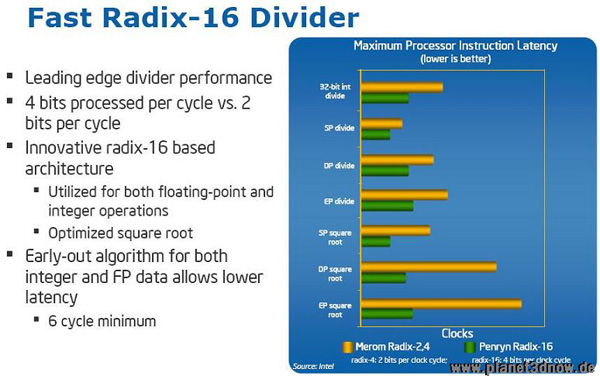

對比Intel的前進的步伐,AMD其實還是慢了許多,因為Intel早在酷睿時代的Penryn架構上就已經採用radix-16除法器了,每週期指令數從原來的2條一下子提高到4條,數據延遲更低,浮點單元以及整數單元都可以從中受益。

分析認為AMD之所以沒有採用radix-16而用了折衷的radix-8,是因為模塊化結構中FP浮點單元被兩個整數單元共享,radix-16過於復雜,成本更高。

架構上的設計變化太過學術化,AMD的模塊化CPU理念先進,但是第一代CPU表現並不太好,既有工藝上的掣肘也有架構設計上的不足,希望到了Steamroller這一代能更成熟些。

來源:http://www.expreview.com/18614.html

有關壓路機的架構設計目前還是捕風捉影的階段,日前AMD研究部門的David M. Russinoff發布的一篇論文中證實了Steamroller將會採用radix-8 SRT浮點模塊,每週期運行指令將從目前的radix- 4單元的2條提高到3條。

Steamroller改變的是CPU中除法器(Divider)單元的設計, 有興趣的可以參考wiki的解釋 。 David M. Russinoff參與了Llano APU的設計,其DIV單元與前代K10沒有DIV硬件支持的設計有所不同,推土機繼承了K10的設計,FMAC(浮點累積乘單元)中的除法器功能有限。 現在Steamroller的設計類似Llano,當然不會是100%相同,因為它使用的是radix-8而非Llano的radix-4,每週期執行的指令數從2條提高到了3條。

對比Intel的前進的步伐,AMD其實還是慢了許多,因為Intel早在酷睿時代的Penryn架構上就已經採用radix-16除法器了,每週期指令數從原來的2條一下子提高到4條,數據延遲更低,浮點單元以及整數單元都可以從中受益。

分析認為AMD之所以沒有採用radix-16而用了折衷的radix-8,是因為模塊化結構中FP浮點單元被兩個整數單元共享,radix-16過於復雜,成本更高。

架構上的設計變化太過學術化,AMD的模塊化CPU理念先進,但是第一代CPU表現並不太好,既有工藝上的掣肘也有架構設計上的不足,希望到了Steamroller這一代能更成熟些。

來源:http://www.expreview.com/18614.html